# Middlesex University Research Repository:

an open access repository of Middlesex University research

http://eprints.mdx.ac.uk

Johnstone, Kevin Kennedy, 1991.

On the nature and effect of power distribution noise in CMOS digital integrated circuits.

Available from Middlesex University's Research Repository.

## Copyright:

Middlesex University Research Repository makes the University's research available electronically.

Copyright and moral rights to this thesis/research project are retained by the author and/or other copyright owners. The work is supplied on the understanding that any use for commercial gain is strictly forbidden. A copy may be downloaded for personal, non-commercial, research or study without prior permission and without charge. Any use of the thesis/research project for private study or research must be properly acknowledged with reference to the work's full bibliographic details.

This thesis/research project may not be reproduced in any format or medium, or extensive quotations taken from it, or its content changed in any way, without first obtaining permission in writing from the copyright holder(s).

If you believe that any material held in the repository infringes copyright law, please contact the Repository Team at Middlesex University via the following email address: <a href="mailto:eprints@mdx.ac.uk">eprints@mdx.ac.uk</a>

The item will be removed from the repository while any claim is being investigated.

# ON THE NATURE AND EFFECT OF POWER DISTRIBUTION NOISE IN CMOS DIGITAL INTEGRATED CIRCUITS

A thesis submitted to the Council for National Academic Awards

by

Kevin Kennedy Johnstone B.Sc.(Edin), M.Sc.(Edin)

in partial fulfilment of the requirements for the degree of

**Doctor of Philosophy**

| ,                     | y942829x                            |

|-----------------------|-------------------------------------|

| SITE HE               | MIDDLESEX<br>POLYTECHNIC<br>LIBRARY |

| JulioSION<br>No.      | 71850384                            |

| CLASS<br>No.          | 621.38224 JOH                       |

| SPECIAL<br>COLLECTION | Thesis<br>Glection                  |

November 1991

Middlesex Polytechnic

# **Table of Contents**

| List of F | iguresvi                                 |

|-----------|------------------------------------------|

| Abstract  | ix                                       |

| Acknow    | ledgementsxii                            |

|           |                                          |

| Introdu   | ction                                    |

| :         | 1. Research Objectives1                  |

| 2         | 2. Scope of Thesis                       |

| 3         | 3. Thesis Structure2                     |

| 4         | 1. Statement of Originality              |

| 1. Tech   | nological Constraints                    |

| ]         | 1.1 Introduction4                        |

| ]         | 1.2 Interconnect Modelling               |

|           | 1.2.1 Interconnect Scaling4              |

|           | 1.2.2 Distributed RC lines5              |

|           | 1.2.3 Transmission Lines8                |

| ]         | .3 Clock Distribution                    |

|           | 1.3.1 Clock Skew                         |

|           | 1.3.2 Locally Synchronous Distribution12 |

|           | 1.3.3 The H-tree Distribution            |

| ]         | .4 Packaging Technology                  |

|           | 1.4.1 The Dual-in-Line Package14         |

|           | 1.4.2 The Pin Grid Array15               |

|           | 1.4.3 Surface Mounting15                 |

|           | 1.4.4 Wire Bonding16                     |

|           | 1.4.5 Tape-automated Bonding16           |

|           | 1.4.6 "Flip-chip" Mounting17             |

|           | 1.4.7 Thermal Properties17               |

|       | 1.5 Power Distribution                                                 |

|-------|------------------------------------------------------------------------|

|       | 1.5.1 Simultaneous Switching Noise18                                   |

|       | 1.5.2 Noise Reduction20                                                |

|       | 1.6 Conclusions22                                                      |

|       |                                                                        |

| 2. Po | ower Distribution Noise Analyses                                       |

|       | 2.1 Introduction                                                       |

|       | 2.2 The Delta-I Simultaneous Switching Problem23                       |

|       | 2.3 Ground Bounce Control in CMOS Integrated Circuits 24               |

|       | 2.4 Power Bus Transients in Very High Speed Logic Systems25            |

|       | 2.5 Noise Generation Analysis and Noise-Suppression  Design Techniques |

|       | 2.6 A CMOS Mainframe Processor with 0.5um Channel Length30             |

|       | 2.7 Conclusions31                                                      |

|       |                                                                        |

|       |                                                                        |

| 3. Po | wer Distribution Noise in an Array-based Architecture                  |

|       | 3.1 Introduction34                                                     |

|       | 3.2 Architectural Overview                                             |

|       | 3.2.1 Systolic Architectures: the Basic Principle34                    |

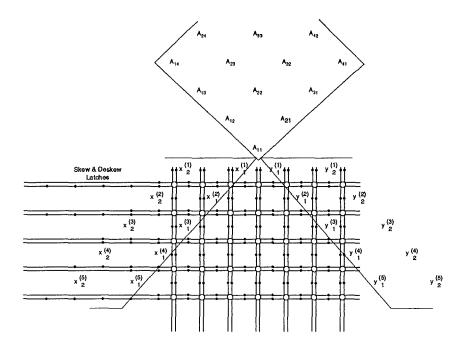

|       | 3.2.2 A Bit-level Systolic Array for Matrix- Vector Multiplication36   |

|       | 3.2.3 A Systolic Array for Correlation37                               |

|       | 3.2.4 An "efficient" Systolic Array for Distance  Computation39        |

|       | 3.2.5 Conclusions42                                                    |

|       | 3.3 The Development of a Simulation Mode                               |

|       | 3.3.1 Overview of Requirements42                                       |

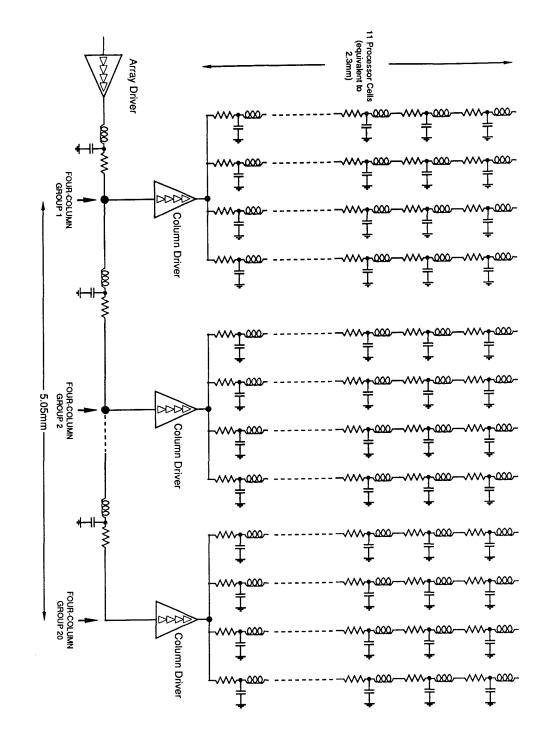

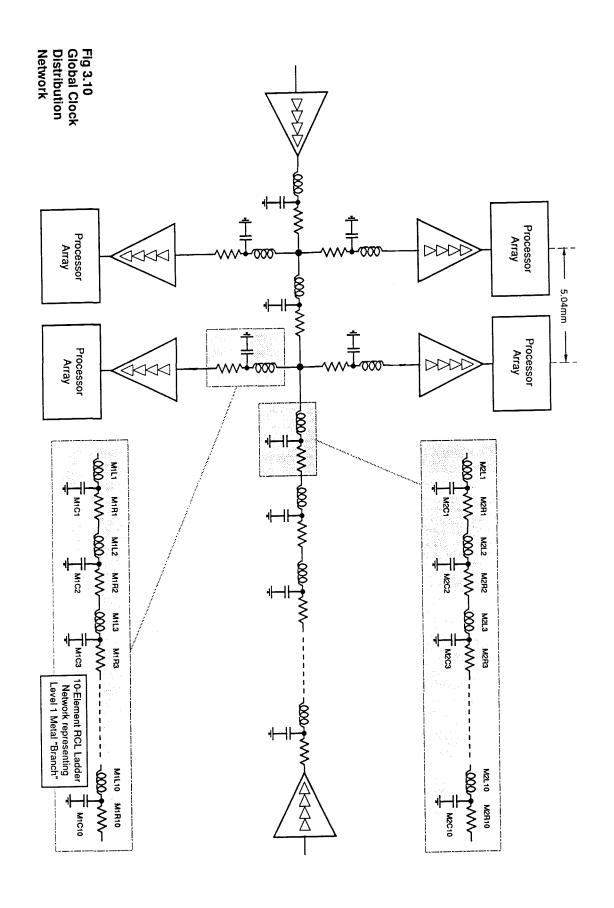

|       | 3.3.2 Clock Distribution Modelling43                                   |

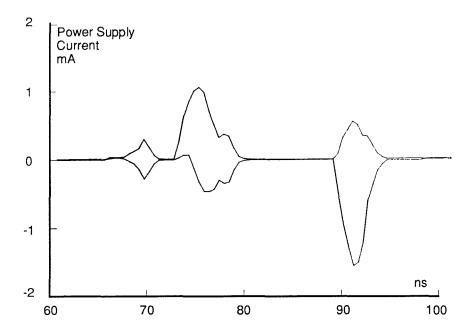

|       | 3.3.3 Current Flow Modelling44                                         |

|       | 3.3.4 Synthesising an Array52                                          |

|       | 3.3.5 The Power Distribution Network54                                 |

|        | 3.3.6 Noise Predictions58                                |

|--------|----------------------------------------------------------|

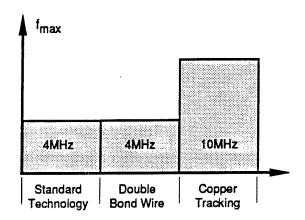

|        | 3.3.7 Non-standard Technology64                          |

|        | 3.4 Performance Implications                             |

|        | 3.4.1 Assessment Methodology65                           |

|        | 3.4.2 Performance Assessment66                           |

|        | 3.5 Noise Model Sensitivity                              |

|        | 3.5.1 Assumption-related Issues69                        |

|        | 3.5.2 Relative Sensitivity70                             |

|        | 3.6 Conclusions                                          |

|        | 3.6.1 Simulation Model72                                 |

|        | 3.6.2 Performance Limitations73                          |

|        |                                                          |

| 4. Pov | ver Distribution Noise in a Non-array-based Architecture |

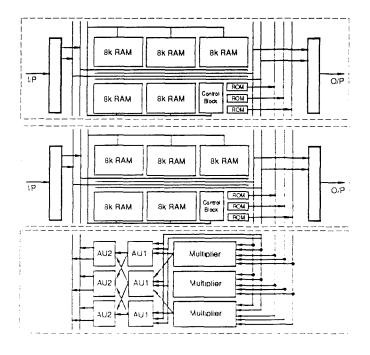

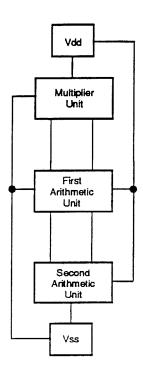

|        | 4.1 Introduction84                                       |

|        | 4.2 Architectural Overview85                             |

|        | 4.3 The Processor Block                                  |

|        | 4.3.1 Block Structure85                                  |

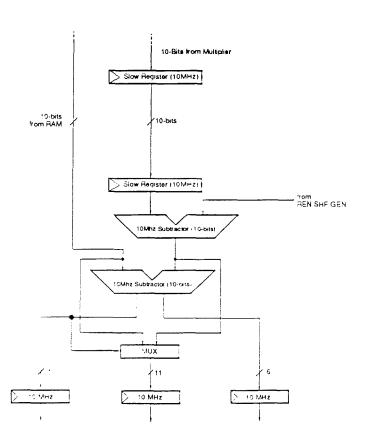

|        | 4.3.2 The Multiplier85                                   |

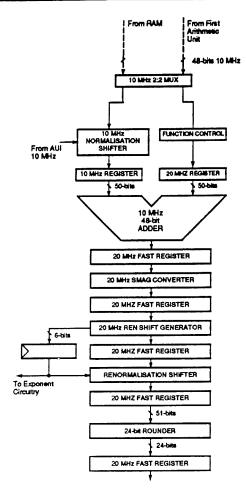

|        | 4.3.2.1 The Mantissa Sub-block85                         |

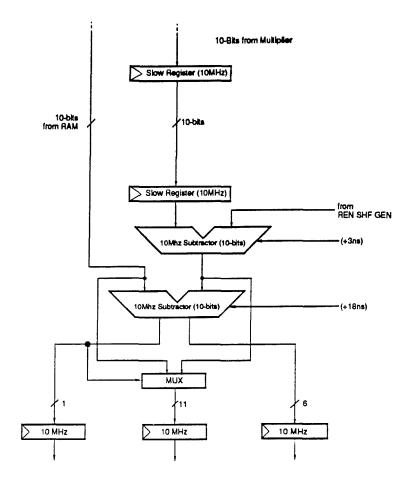

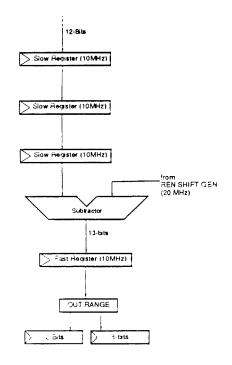

|        | 4.3.2.2 The Exponent Sub-block90                         |

|        | 4.3.3 The Power Distribution Network92                   |

|        | 4.3.4 The First Arithmetic Unit94                        |

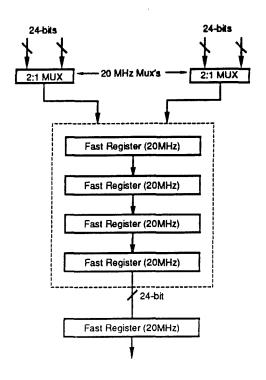

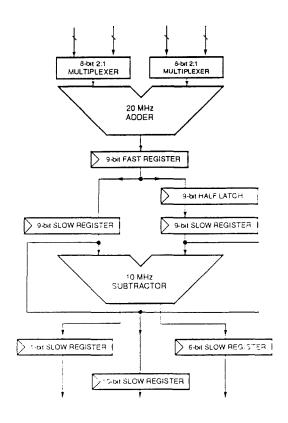

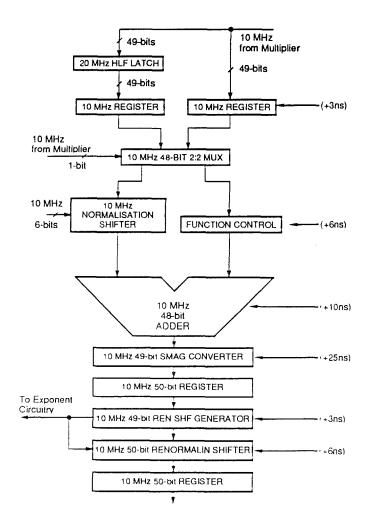

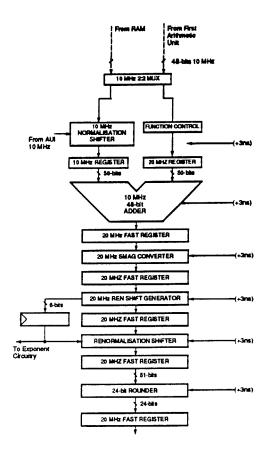

|        | 4.3.4.1 The Mantissa Sub-block94                         |

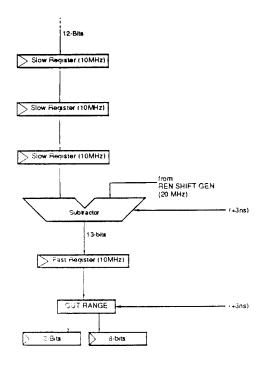

|        | 4.3.4.2 The Exponent Sub-block96                         |

|        | 4.3.5 The Second Arithmetic Unit100                      |

|        | 4.3.5.1 The Mantissa Sub-block100                        |

|        | 4.3.5.2 The Exponent Sub-block100                        |

|        | 4.4 The Memory Block                                     |

|        | 4.4.1 Block Structure102                                 |

|        | 4.4.2 The I/O Driver103                                  |

|        | 4.4.3 The Row Substitution Circuit103                    |

|                | 4.4.4 The blume Precharge Drivers105                      |

|----------------|-----------------------------------------------------------|

|                | 4.4.5 The Precharge Circuits                              |

|                | 4.4.6 The Address Input Drivers104                        |

|                | 4.4.7 The Output Circuitry105                             |

|                | 4.4.8 The Remaining Circuit Blocks105                     |

|                | 4.4.9 The Power Distribution Network105                   |

| 4.5 Th         | e Control, ROM and I/O Blocks                             |

|                | 4.5.1 The Control Block106                                |

|                | 4.5.2 The ROM Blocks107                                   |

|                | 4.5.3 The I/O Blocks107                                   |

|                | 4.5.4 The Power Distribution Network107                   |

| 4.6 Per        | rformance of Processor Reticle Power Distribution Network |

|                | 4.6.1 Noise Model110                                      |

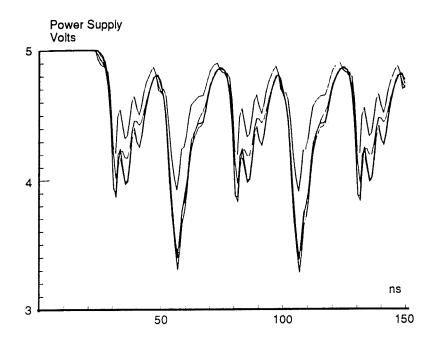

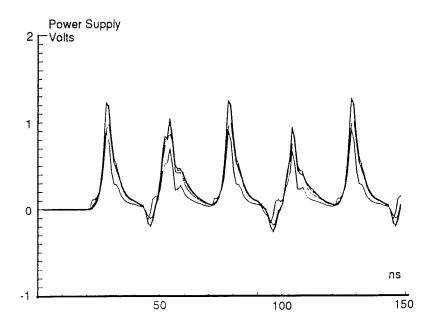

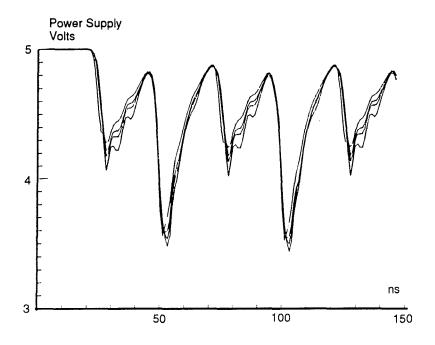

|                | 4.6.2 Noise Predictions                                   |

|                | 4.6.3 Non-standard Technology118                          |

|                | 4.6.4 Performance Implications118                         |

|                | 4.6.5 Noise Model Sensitivity119                          |

| 4.7 Per        | formance of Memory Reticle Power Distribution Network     |

|                | 4.7.1 Noise Model                                         |

|                | 4.7.2 Noise Predictions                                   |

|                | 4.7.3 Non-standard Technology125                          |

|                | 4.7.4 Performance Implications125                         |

|                | 4.7.5 Noise Model Sensitivity125                          |

| 4.8 Co         | nclusions                                                 |

|                | 4.8.1 Simulation Model                                    |

|                | 4.8.2 Performance Limitations                             |

|                |                                                           |

| 5. Transient I | atch-up and Electromigration                              |

|                | unsient Latch-up                                          |

|                | 5.1.1 Introduction129                                     |

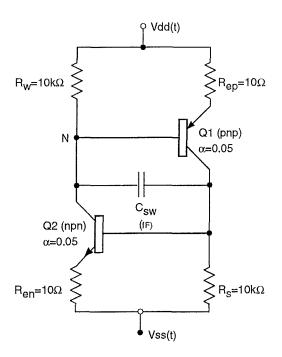

|                | 5.1.2 Simulation Model and Methodology129                 |

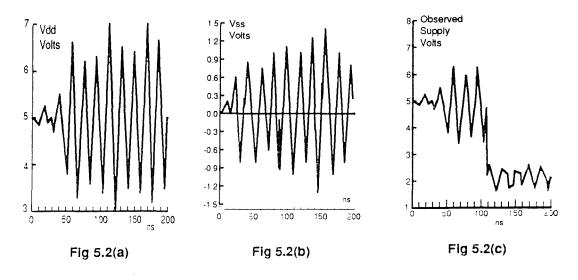

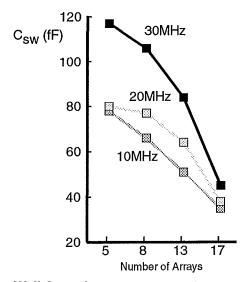

|              | 5.1.3 Results                   | 131 |

|--------------|---------------------------------|-----|

|              | 5.1.4 Conclusions               | 131 |

| 5.2 E        | Electromigration                |     |

|              | 5.2.1 Introduction              | 134 |

|              | 5.2.2 Electromigration Analysis | 134 |

|              | 5.2.3 Results                   | 134 |

|              | 5.2.4 Conclusions               | 137 |

|              |                                 |     |

| Conclusions  | 5                               |     |

|              | 1. Noise Modelling Methodology  | 138 |

|              | 2. The Nature of the Noise      | 139 |

|              | 3. A More Automated Approach    | 140 |

|              | 4. Predicted Consequences       | 140 |

| References . |                                 | 142 |

# List of Figures

# Chapter 1

| Fig 1.1  | Interconnect Capacitance - Area & Periphery Terms          |

|----------|------------------------------------------------------------|

| Fig 1.2  | Interconnect Capacitance vs Interconnect Width/Oxide       |

|          | Thickness                                                  |

| Fig 1.3  | T-network & Ladder Network distributed RC models           |

| Fig 1.4  | Error of Simulated Results Relative to Theoretical as a    |

|          | Function of Frequency                                      |

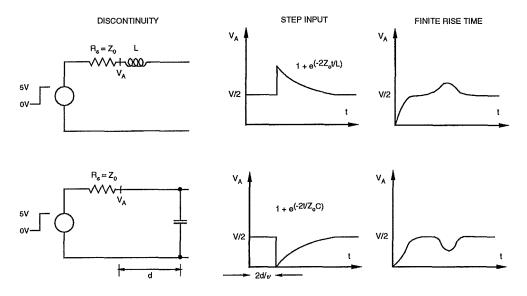

| Fig 1.5  | Inductive & Capacitive Discontinuities                     |

| Fig 1.6  | Critical Transmission Line Lengths                         |

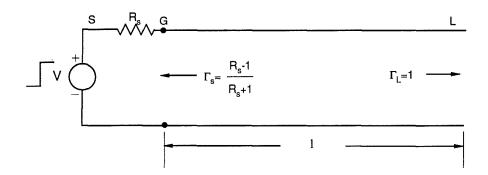

| Fig 1.7  | Unterminated Transmission Line driven by a Source          |

|          | Resistance Rs                                              |

| Fig 1.8  | Lossy Transmission Line Model                              |

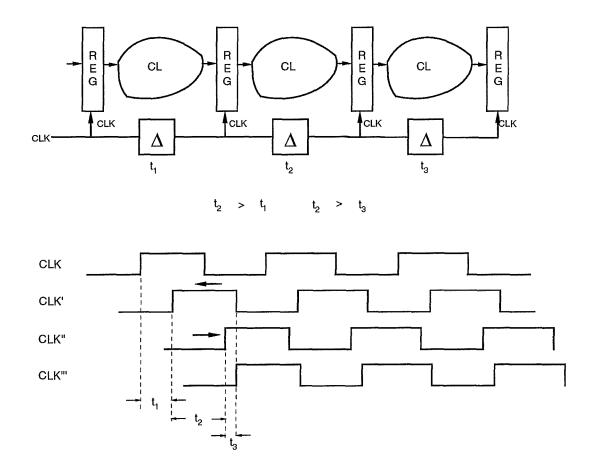

| Fig 1.9  | Clock Distribution Tuning                                  |

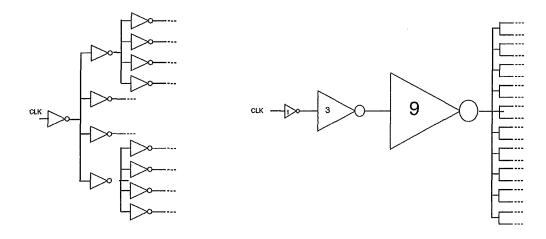

| Fig 1.10 | Multiple Driver Distribution Scheme                        |

| Fig 1.11 | Successively Higher Gain Driver Distribution Scheme        |

| Fig 1.12 | H-tree Clock Distribution Scheme                           |

| Fig 1.13 | Package Electrical Parasitics                              |

| Fig 1.14 | Simplified Model of a CMOS Circuit, Package & Power Supply |

| Fig 1.15 | On-chip & Off-chip Supply Decoupling Paths                 |

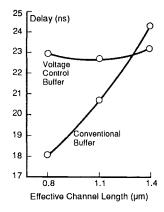

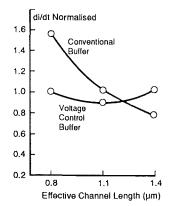

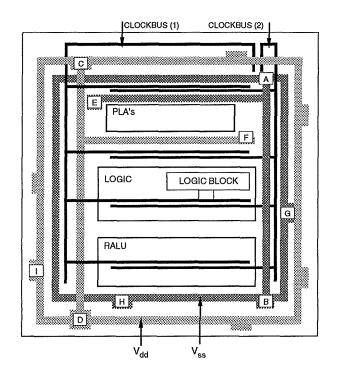

| Fig 2.1  | Delay vs Channel Length                                       |

|----------|---------------------------------------------------------------|

| Fig 2.2  | di/dt vs Channel Length                                       |

| Fig 2.3  | Equivalent Circuit                                            |

| Fig 2.4  | Computed Waveforms - High Speed CMOS Circuit Model            |

| Fig 2.5  | Computed Waveforms for 50% Switching showing Excitation of    |

|          | the 15MHz Power Bus Resonance                                 |

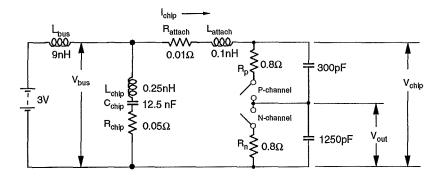

| Fig 2.6  | Clockbus & Powerbus Structure of BELLMAC-32A                  |

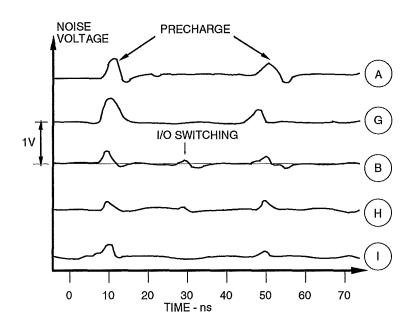

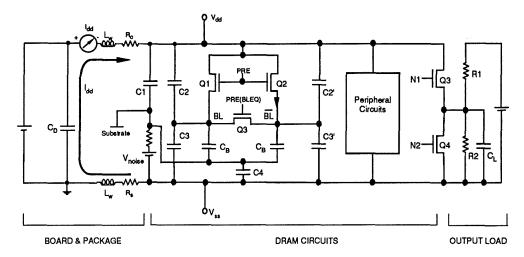

| Fig 2.7  | Noise Voltage vs Time                                         |

| Fig 2.8  | Equivalent Circuit for the Voltage-bouncing Noise             |

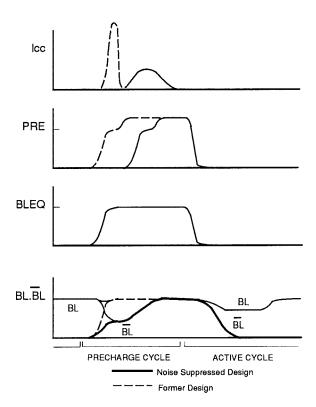

| Fig 2.9  | Operating Peak Current Icc & Control Signals for bit-line     |

|          | precharging circuitry                                         |

| Fig 2.10 | Transistor Count                                              |

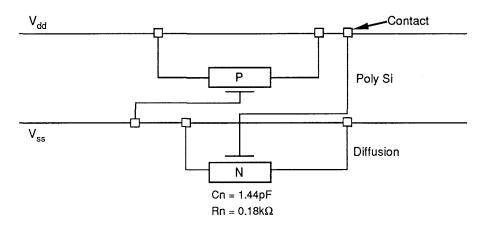

| Fig 2.11 | Layout & Circuit Schematic of on-chip decoupling capacitors   |

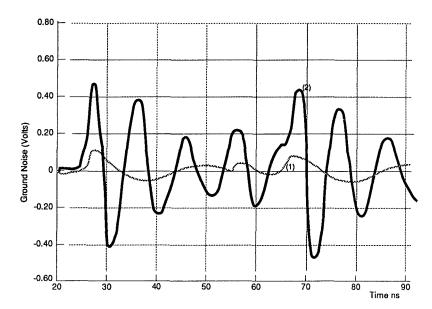

| Fig 2.12 | Chip Ground Noise with (1) and without (2) on-chip decoupling |

|          | capacitors                                                    |

|          |                                                               |

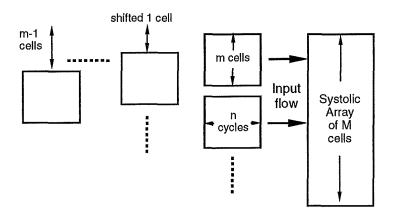

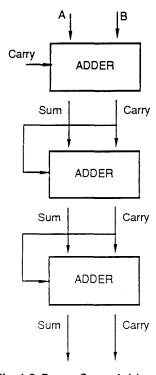

| Fig 3.1     | Basic Principle of Systolic Array                        |

|-------------|----------------------------------------------------------|

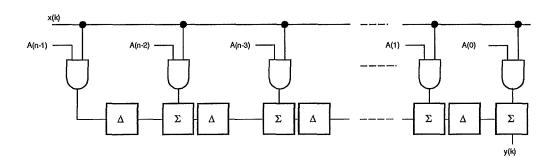

| Fig 3.2     | Four-point Bitslice Transform                            |

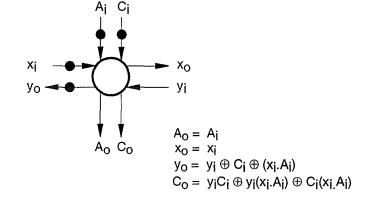

| Fig 3.3     | Constituent Processor Cell Logic Function                |

| Fig 3.4     | Equivalent Architecture of Systolic Correlator           |

| Fig 3.5     | Bit-Serial Operation of Systolic Correlator              |

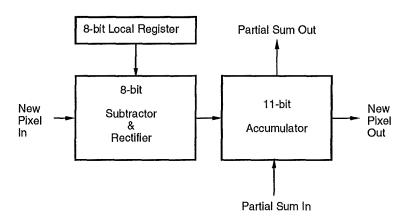

| Fig 3.6     | Cell for Motion Detector                                 |

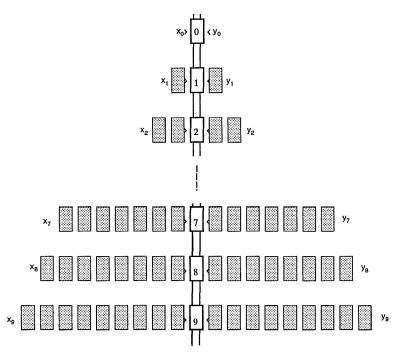

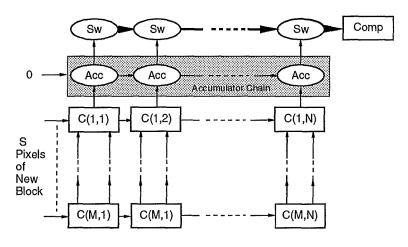

| Fig 3.7     | Matrix of Processor Cells                                |

| Fig 3.8     | Input Data Flow                                          |

| Fig 3.9     | Local Clock Distribution Netowrk                         |

| Fig 3.10    | Global Clock Distribution Network                        |

| Fig 3.11    | Global Clock Skew vs Array Size                          |

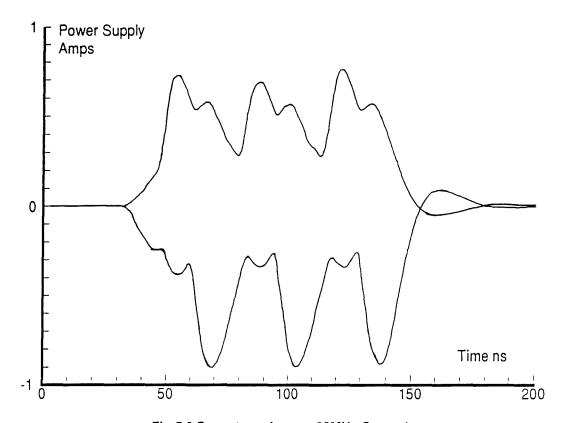

| Fig 3.12    | Supply Current vs Time                                   |

| Fig 3.13    | Processor Cell Load Equivalent Circuits                  |

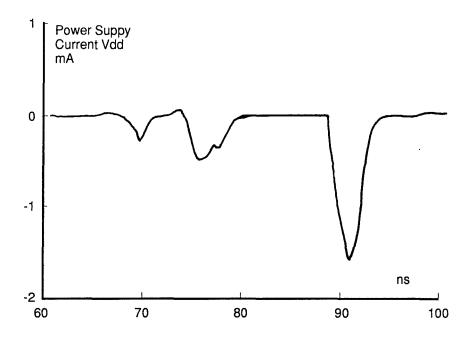

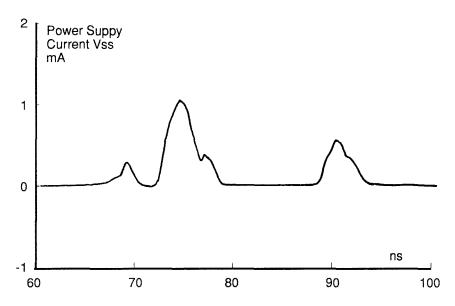

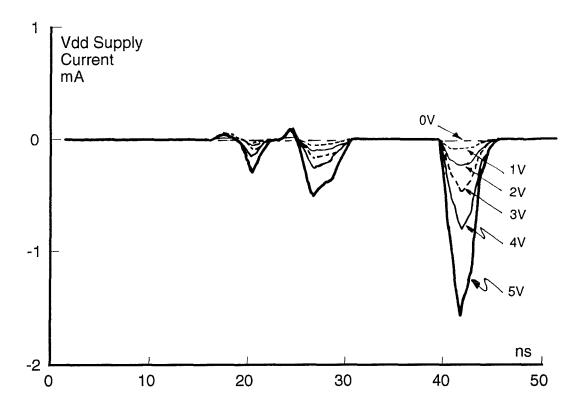

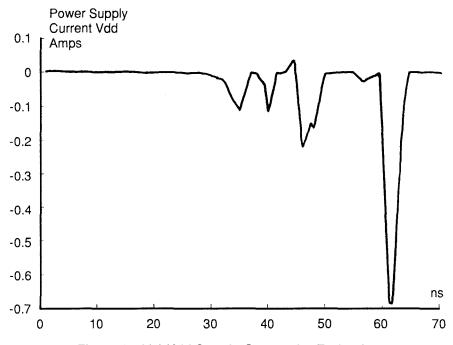

| Fig 3.14(a) | Processor Cell Power Supply Current (Vdd)                |

| Fig 3.14(b) | Processor Cell Power Supply Current (Vss)                |

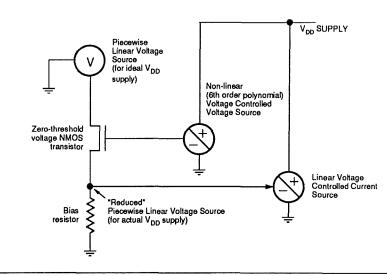

| Fig 3.15    | Equivalent Circuit with Negative Feedback                |

| Fig 3.16    | Supply Current vs Supply Voltage for modified Equivalent |

|             | Circuit                                                  |

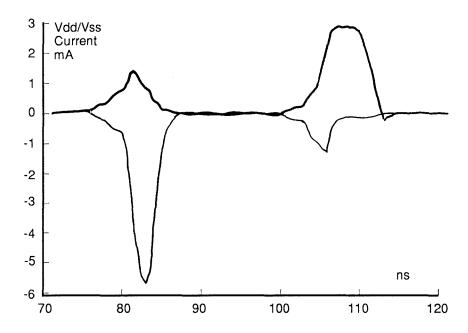

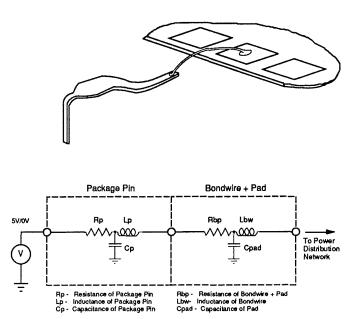

| Fig 3.17    | Vdd/Vss Current for Column Driver                        |

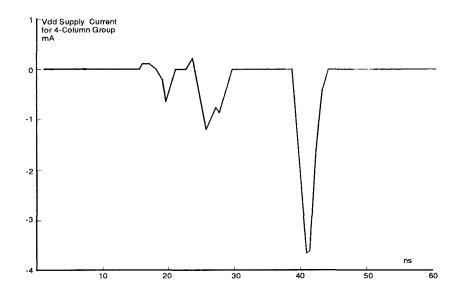

| Fig 3.18(a) | Vdd Supply Current for Four Column Group                 |

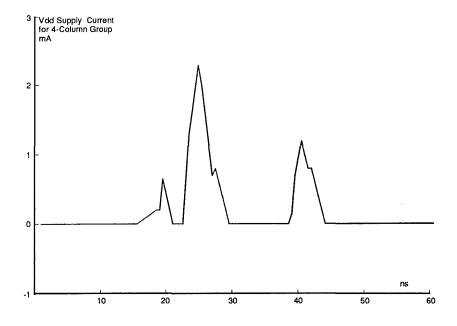

| Fig 3.18(b) | Vss Supply Current for Four Column Group                 |

| Fig 3.19(a) | Vdd Supply Current for Entire Array                      |

| Fig 3.19(b) | Vss Supply Current for Entire Array                      |

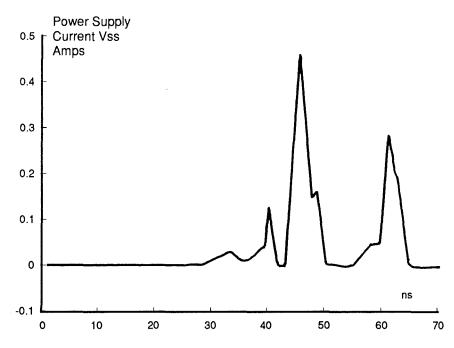

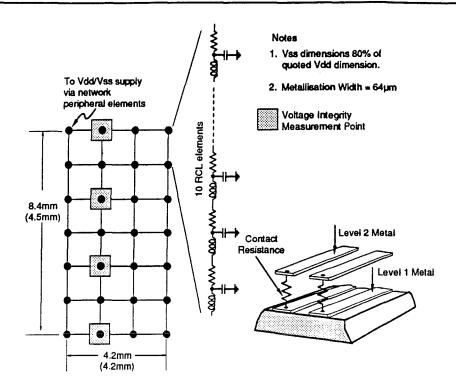

| Fig 3.20    | Power Distribution Network Topology                      |

| Fig 3.21    | Package-related Parasitics                               |

| Fig 3.22    | Voltage Subtractor                                       |

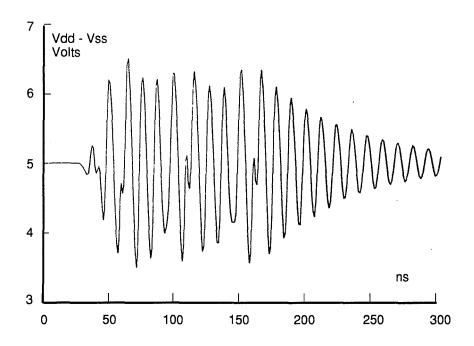

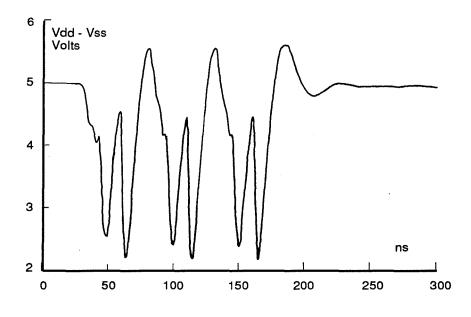

| Fig 3.23    | Instantaneous Difference in Vdd and Vss                  |

|             | Single Array                                             |

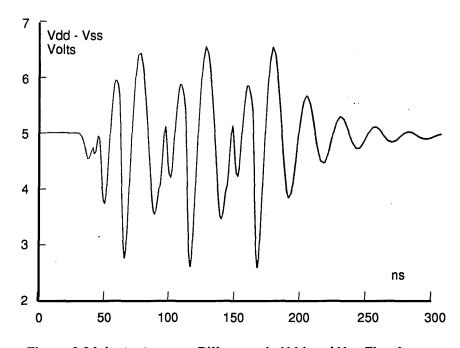

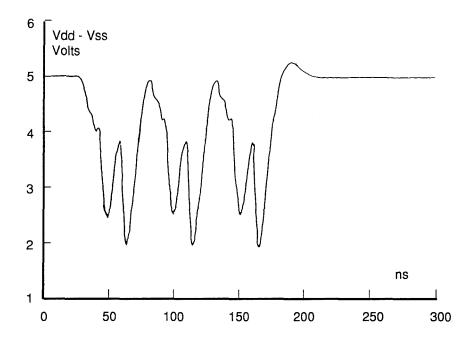

| Fig 3.24    | Instantaneous Difference in Vdd and Vss Five Arrays      |

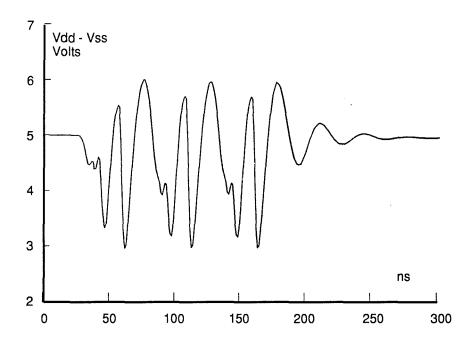

| Fig 3.25    | Instantaneous Difference in Vdd and Vss Eight Arrays     |

| Fig 3.26    | Instantaneous Difference in Vdd and Vss Thirteen Arrays  |

| Fig 3.27    | Instantaneous Difference in Vdd and Vss                  |

|             | Seventeen Arrays                                         |

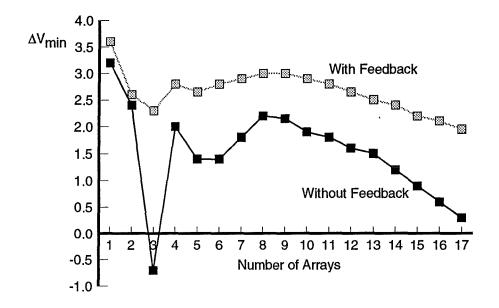

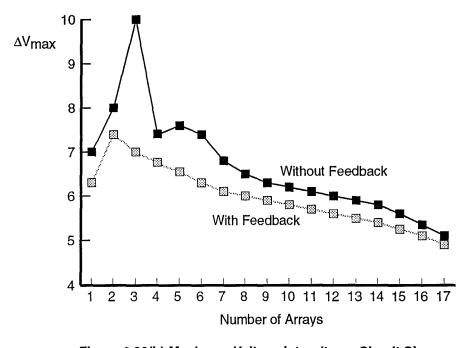

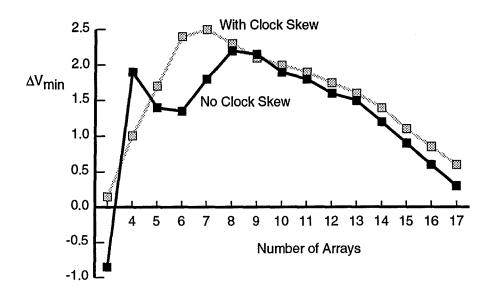

| Fig 3.28(a) | Minimum Voltage Integrity vs Circuit Size                |

| Fig 3.28(b) | Maximum Voltage Integrity vs Circuit Size                |

| Fig 3.29(a) | Global Clock Skew - DVmin                                |

| Fig 3.29(b) | Global Clock Skew - DVmax                                |

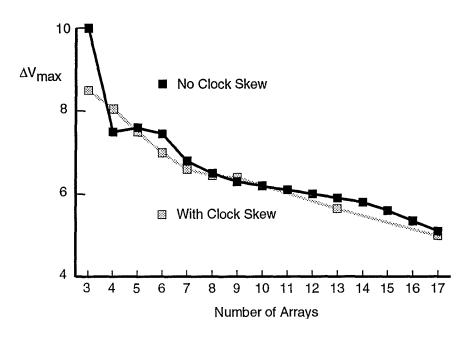

| Fig 3.30    | Maximum & Minimum Voltage Integrity for Non-standard     |

|             | Technologies                                             |

| Fig 3.31    | Processor Cell Inverter Structures                       |

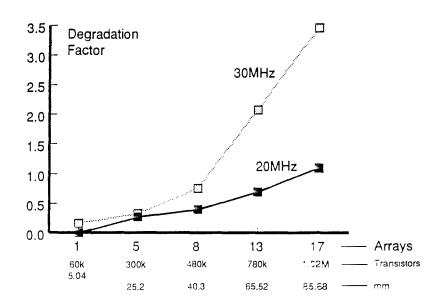

| Fig 3.32    | Gate Delay Degradation for Seventeen Arrays (20MHz)      |

|             |                                                          |

# Chapter 3

| Fig 3.33 | Gate Delay Degradation for Seventeen Arrays (30MHz)      |

|----------|----------------------------------------------------------|

| Fig 3.34 | Relative Fall Time Degradation for Seventeen Arrays      |

|          | operating at 30MHz                                       |

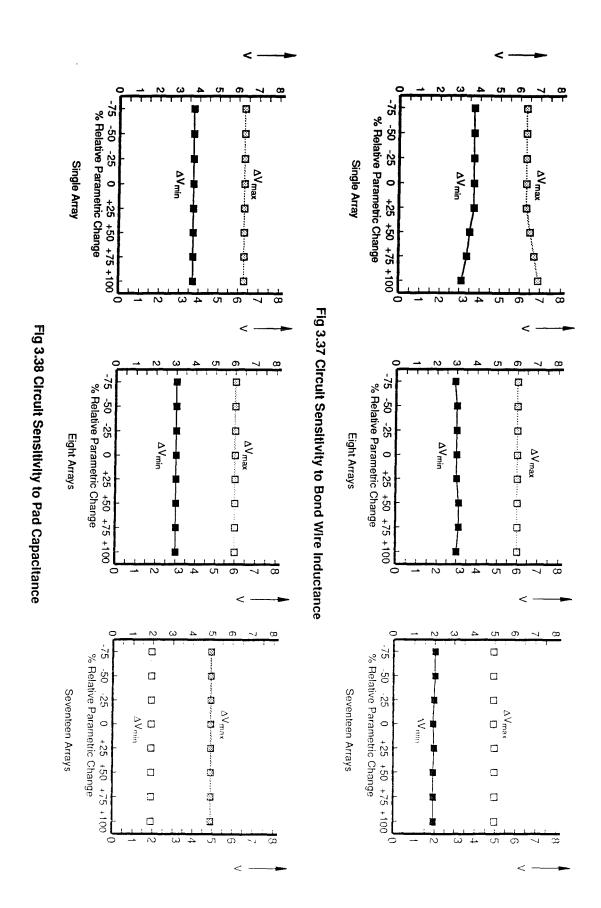

| Fig 3.35 | Circuit Sensitivity to Bond Wire Resistance              |

| Fig 3.36 | Circuit Sensitivity to Bond Wire Capacitance             |

| Fig 3.37 | Circuit Sensitivity to Bond Wire Inductance              |

| Fig 3.38 | Circuit Sensitivity to Pad Capacitance                   |

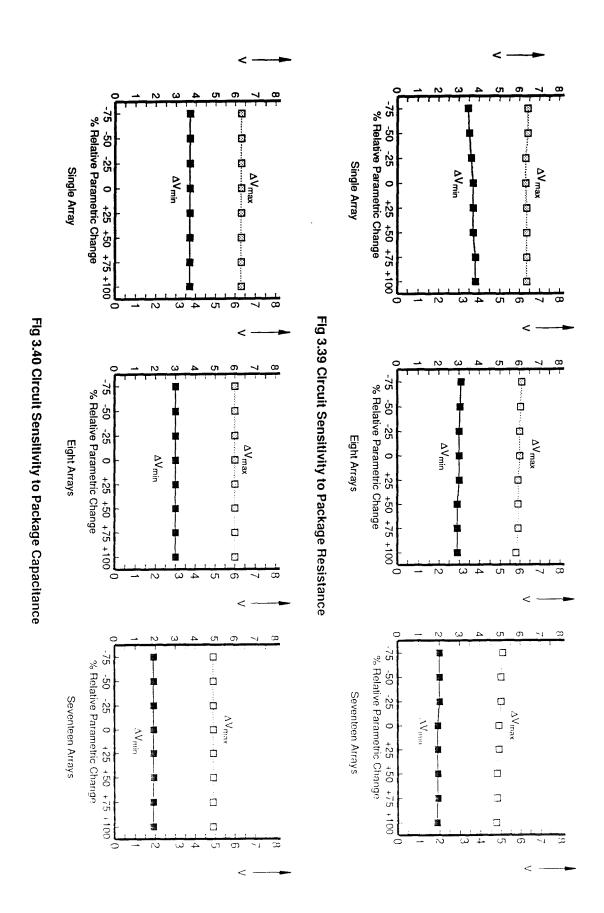

| Fig 3.39 | Circuit Sensitivity to Package Resistance                |

| Fig 3.40 | Circuit Sensitivity to Package Capacitance               |

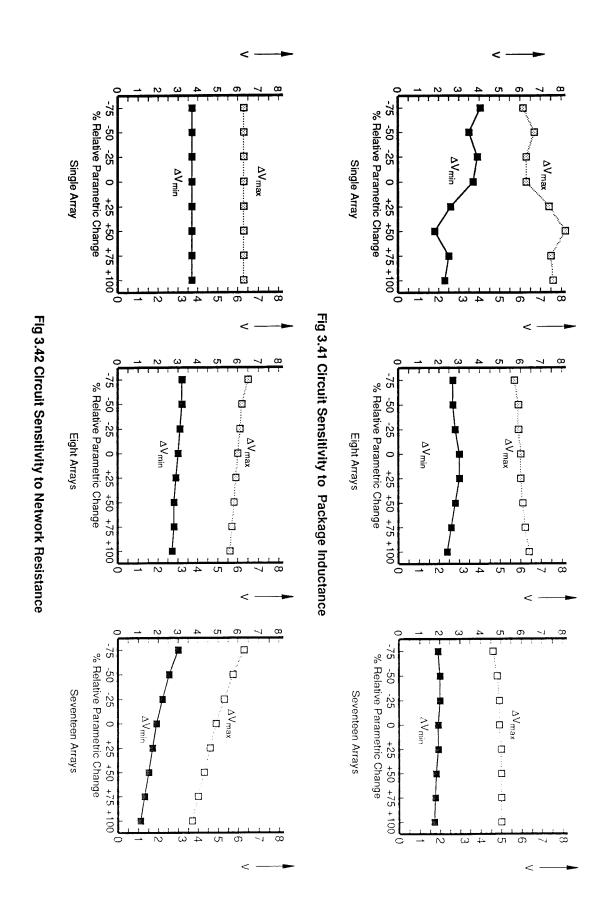

| Fig 3.41 | Circuit Sensitivity to Package Inductance                |

| Fig 3.42 | Circuit Sensitivity to Network Resistance                |

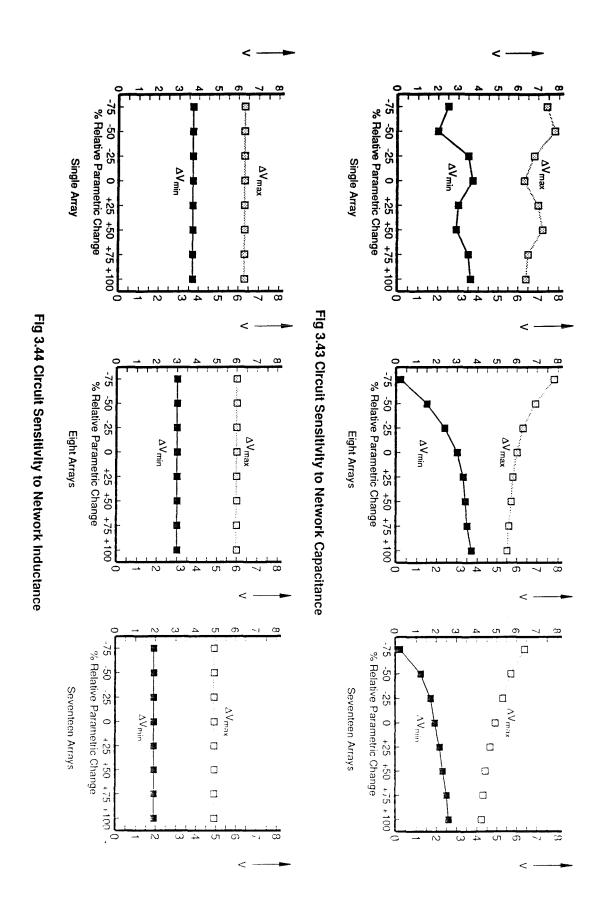

| Fig 3.43 | Circuit Sensitivity to Network Capacitance               |

| Fig 3.44 | Circuit Sensitivity to Network Inductance                |

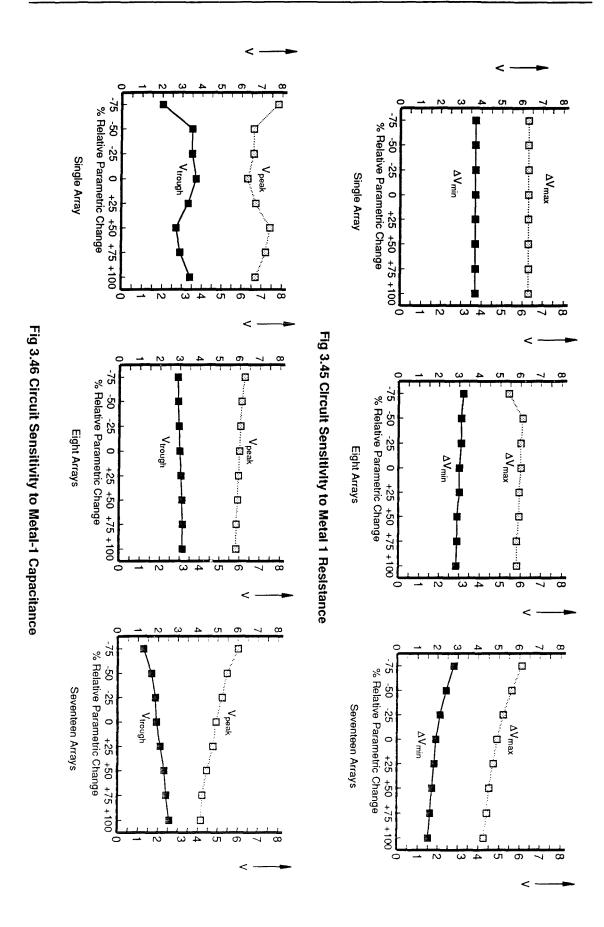

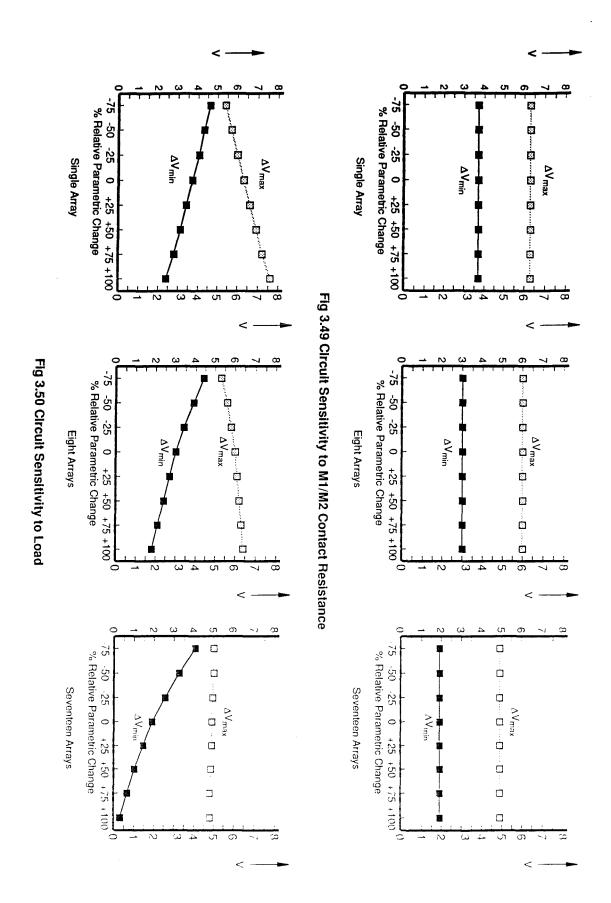

| Fig 3.45 | Circuit Sensitivity to Metal-1 Resistance                |

| Fig 3.46 | Circuit Sensitivity to Metal-1 Capacitance               |

| Fig 3.47 | Circuit Sensitivity to Metal-1 Inductance                |

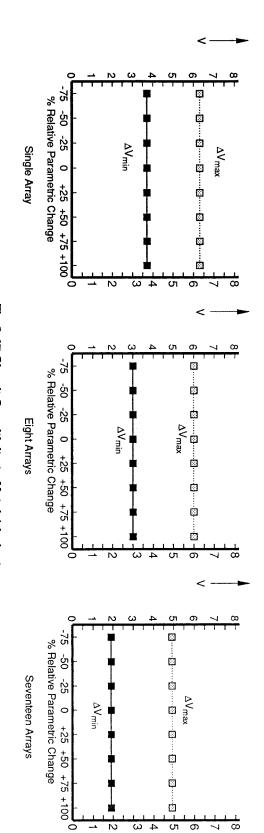

| Fig 3.48 | Relative Circuit Sensitivity to Metal-1/2 Resistance     |

| Fig 3.49 | Circuit Sensitivity to M1/M2 Contact Resistance          |

| Fig 3.50 | Circuit Sensitivity to Load                              |

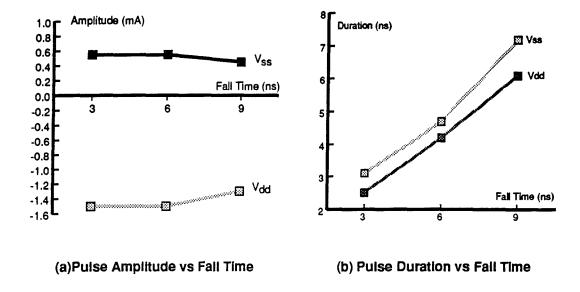

| Fig 3.51 | Sensitivity to Test Vector Transmission Times            |

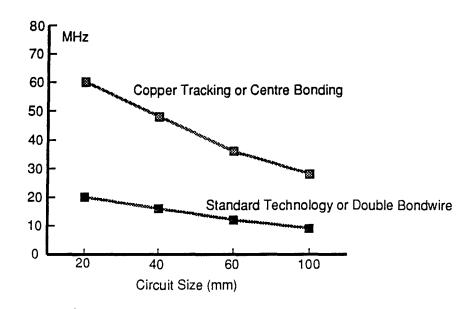

| Fig 3.52 | Fall Time Degradation vs Circuit Size                    |

| Fig 3.53 | Maximum Frequency for Reliable Operation vs Circuit Size |

|          |                                                          |

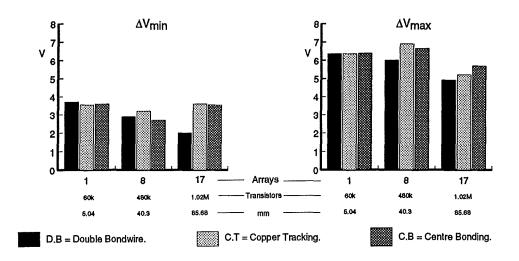

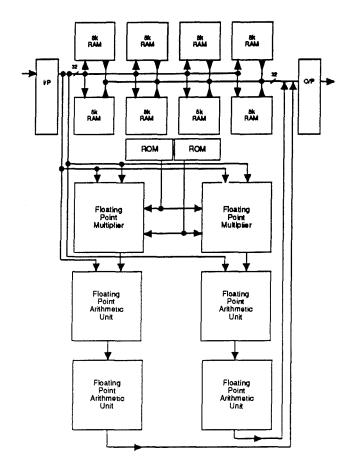

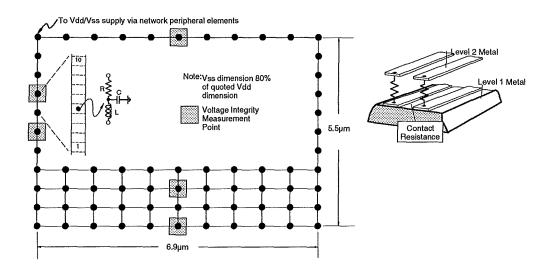

| Fig 4.1     | Functional Block Diagram                              |

|-------------|-------------------------------------------------------|

| Fig 4.2     | Floorplan                                             |

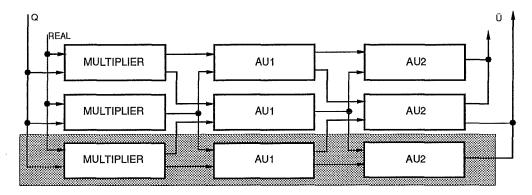

| Fig 4.3     | Processor - Overall Structure & Interconnect Topology |

| Fig 4.4(a)  | Multiplier Unit - Exponent Sub-block                  |

| Fig 4.4(b)  | Multiplier Unit - Mantissa Sub-block                  |

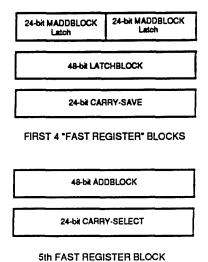

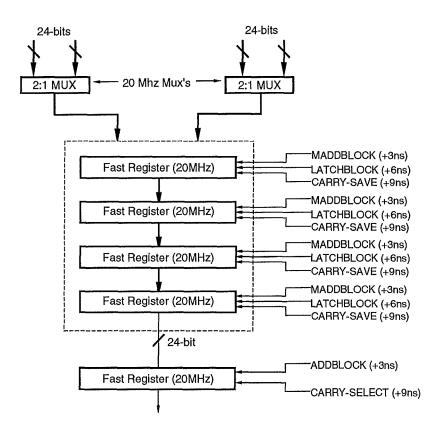

| Fig 4.5     | Internal Structure of 24-Bit Multiplier               |

| Fig 4.6     | Carry-Save Adder "Bitslice"                           |

| Fig 4.7     | Multiplier Unit - Mantissa Sub-block                  |

| Fig 4.8     | Multiplier Unit - Exponent Sub-block                  |

| Fig 4.9     | Multiplier Power Distribution Topology                |

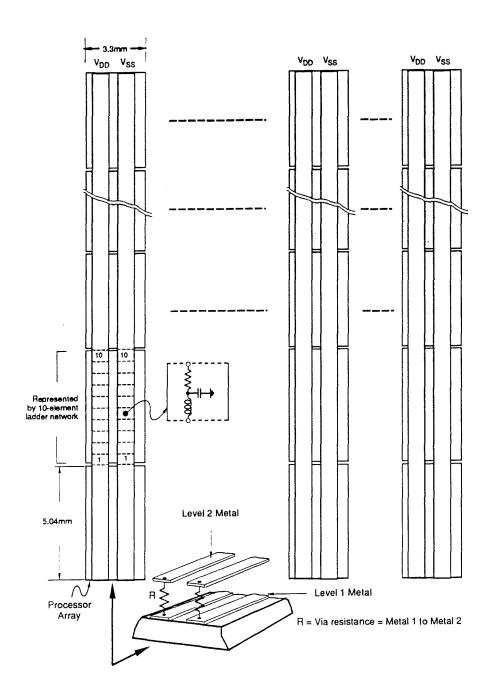

| Fig 4.10    | Package Related Parasitics                            |

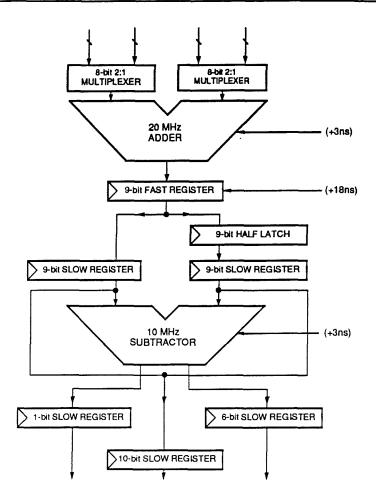

| Fig 4.11(a) | First Arithmetic Unit Exponent Sub-block              |

| Fig 4.11(b) | First Arithmetic Unit Mantissa Sub-block              |

|             |                                                       |

| Fig 4.12         | First Arithmetic Unit-Mantissa Sub-block                       |

|------------------|----------------------------------------------------------------|

| Fig 4.13         | First Arithmetic Unit-Exponent Sub-block                       |

| Fig 4.14(a)      | Second Arithmetic Unit-Mantissa Sub-block                      |

| Fig 4.14(b)      | Second Arithmetic Unit-Exponent Sub-block                      |

| Fig 4.15         | Second Arithmetic Unit-Mantissa Sub-block                      |

| Fig 4.16         | Second Arithmetic Unit-Exponent Sub-block                      |

| Fig 4.17         | 8k RAM Block-Physical Organisation                             |

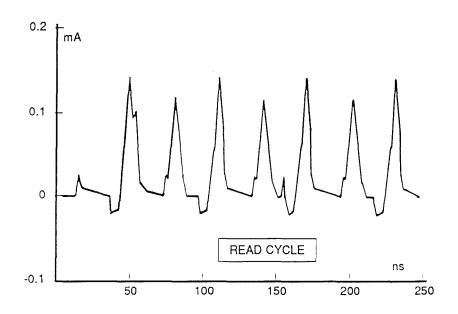

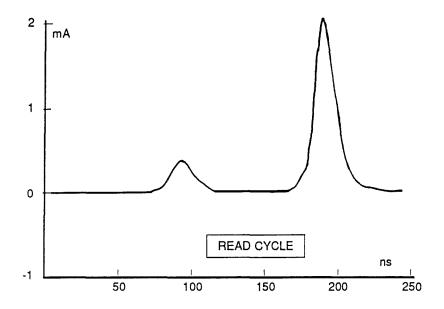

| Fig 4.18(a)      | Vss Bitline Precharge Current- Read Cycle                      |

| Fig 4.18(b)      | Vss Bitline Precharge Current - Write Cycle                    |

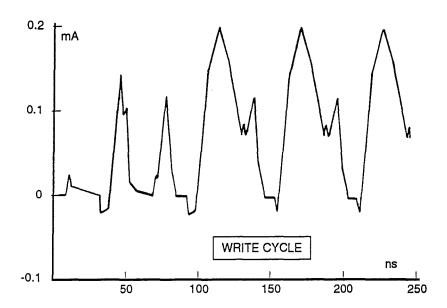

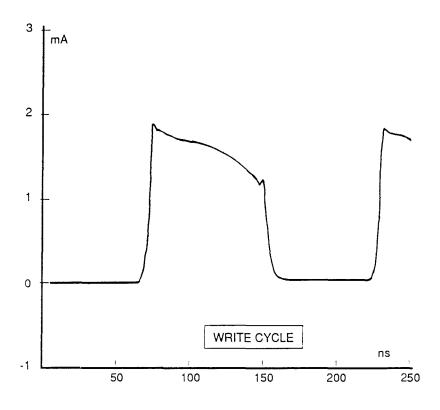

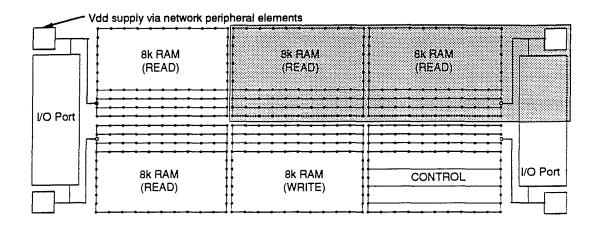

| Fig 4.19         | Power Distribution Network Topology for Memory Reticle         |

| Fig 4.20         | Control Block - Physical Organisation                          |

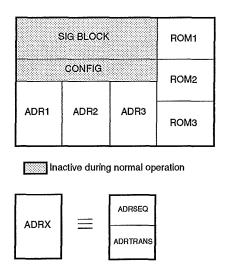

| Fig 4.21(a)      | I/O Port Vss Current-Read Cycle                                |

| Fig 4.21(b)      | I/O Port Vss Current-Write Cycle                               |

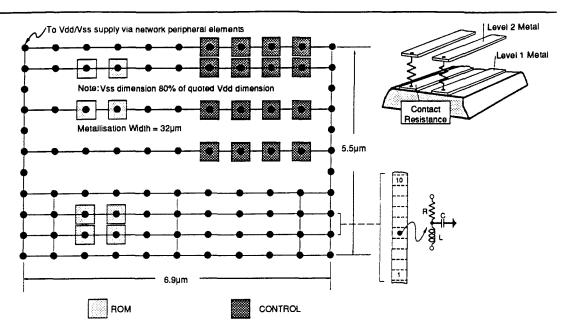

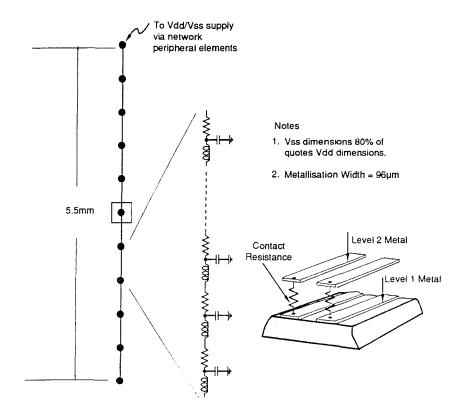

| Fig 4.22         | Distribution Network for Control Block                         |

| Fig 4.23         | Distribution Network for Read & Write Ports                    |

| Fig 4.24         | Power Distribution Network for Processor Slice                 |

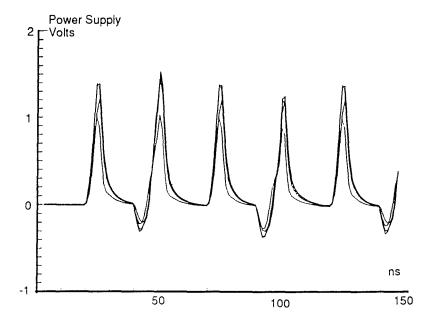

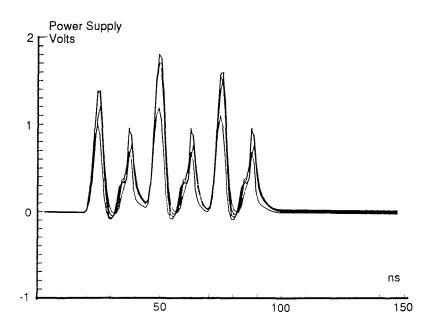

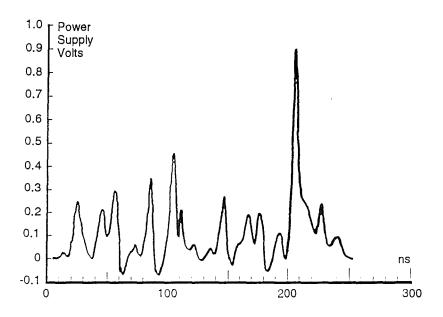

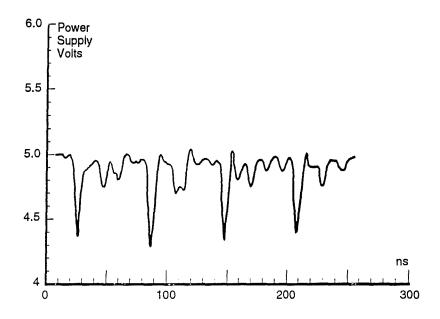

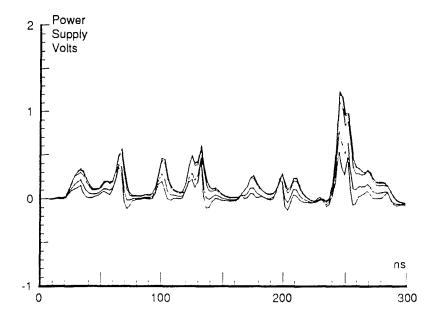

| Fig 4.25         | Noise Predictions for Multiplier Unit within "Processor Slice" |

|                  | (20MHz Operation)                                              |

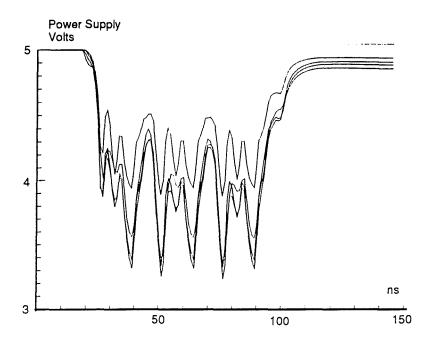

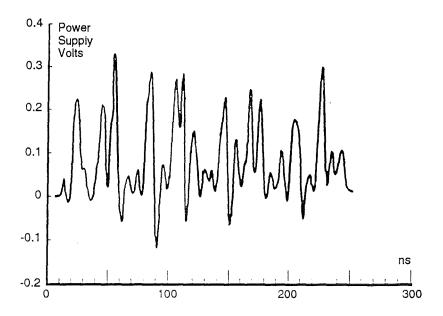

| Fig 4.26         | Noise Predictions for First Arithmetic Unit within 20MHz       |

|                  | Operation "Processor Slice                                     |

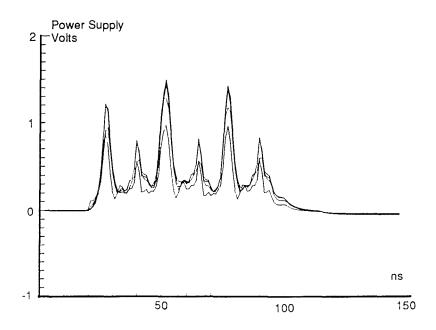

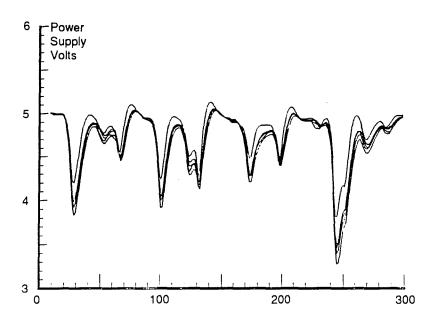

| Fig 4.27         | Noise Predictions for Second Arithmetic Unit within 20MHz      |

|                  | Operation "Processor Slice"                                    |

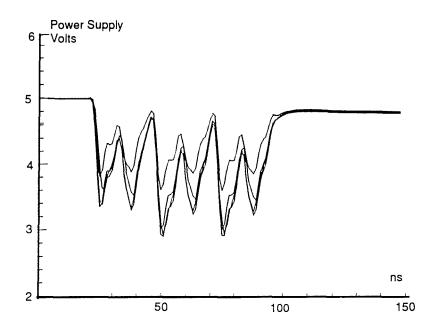

| Fig 4.28         | Noise Predictions for Multiplier Unit without Internal Offsets |

|                  | (20MHz Operation)                                              |

| Fig 4.29         | Noise Predictions for Multiplier Unit within "Processor Slice" |

|                  | (40MHz Operation)                                              |

| Fig 4.30         | Noise Predictions for Multiplier Unit without Internal Offsets |

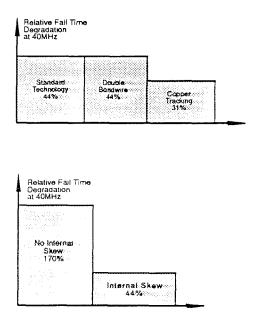

| Figs 4.31 & 4.32 | Relative Fall Time Degradation for Processor Slice             |

| Fig 4.33         | Sensitivity Analysis                                           |

| Fig 4.34         | Memory Reticle Partitioning                                    |

| Fig 4.35         | Noise Predictions for 8k RAM Block during Read Cycle           |

| Fig 4.36         | Noise Predictions for 8k RAM Block during Write Cycle          |

| Fig 4.37         | Noise Predictions for 8k RAM Block within Memory Reticle       |

| Fig 4.38         | Relative Degradation for 8k RAM                                |

| Fig 4.39         | Sensitivity Analysis                                           |

| Fig 4.40         | Fall Time Degradation vs Technology                            |

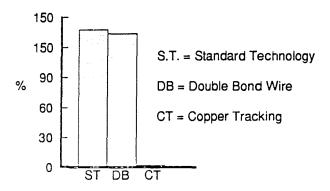

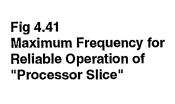

| Fig 4.41         | Maximum Frequency for Reliable Operation of "Processor Slice"  |

| Fig 4.42         | Fall Time Degradation vs Technology                            |

| Fig 4.43         | Maximum Frequency for Reliable Operation of 8k RAM Block       |

| Fig 5.1    | Transient Latch-up Model                                 |  |  |

|------------|----------------------------------------------------------|--|--|

| Fig 5.2    | Simulation of Collapsing Supply Voltage                  |  |  |

| Fig 5.3    | Substrate Well Capacitance necessary to cause Transient  |  |  |

|            | Latch-up                                                 |  |  |

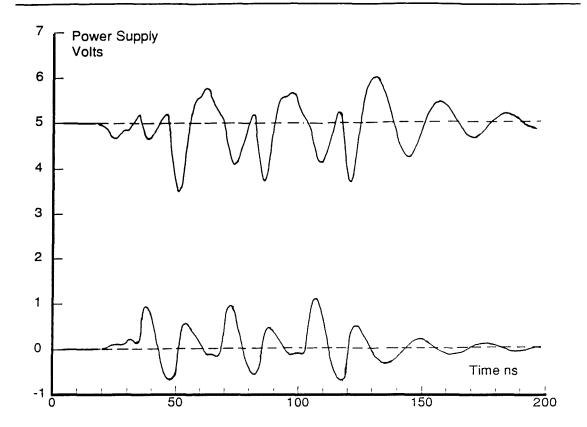

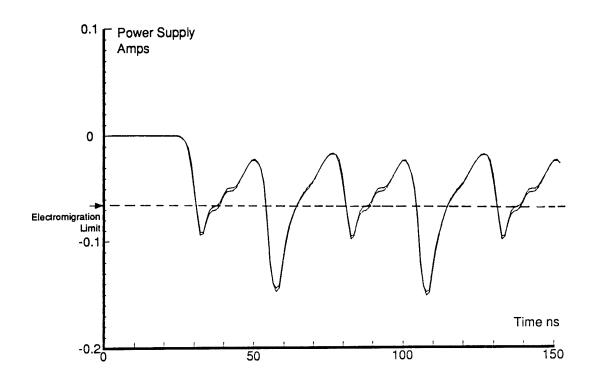

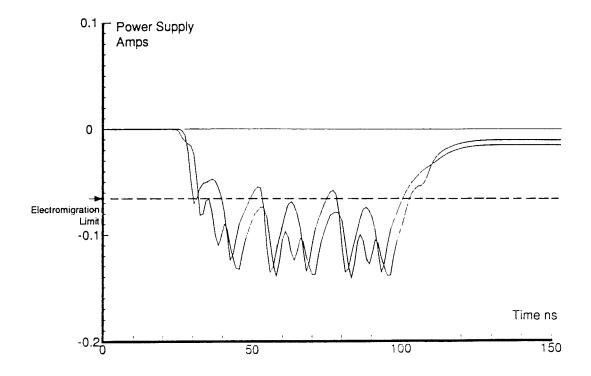

| Fig 5.4(a) | Five Arrays: 30MHz Operation                             |  |  |

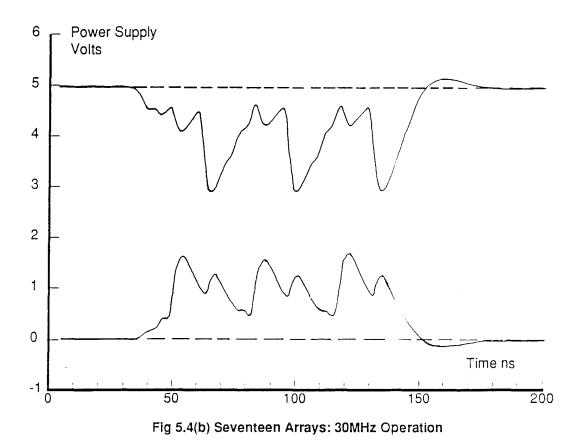

| Fig 5.4(b) | Seventeen Arrays: 30MHz Operation                        |  |  |

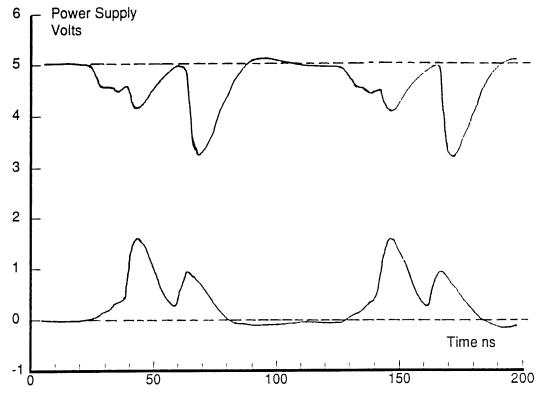

| Fig 5.5(a) | Seventeen Arrays: 10MHz Operation                        |  |  |

| Fig 5.5(b) | Seventeen Arrays: 30MHz Operation                        |  |  |

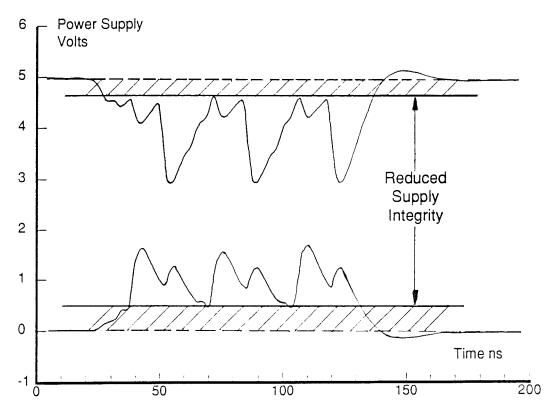

| Fig 5.6    | Seventeen Arrays: 30MHz Operation                        |  |  |

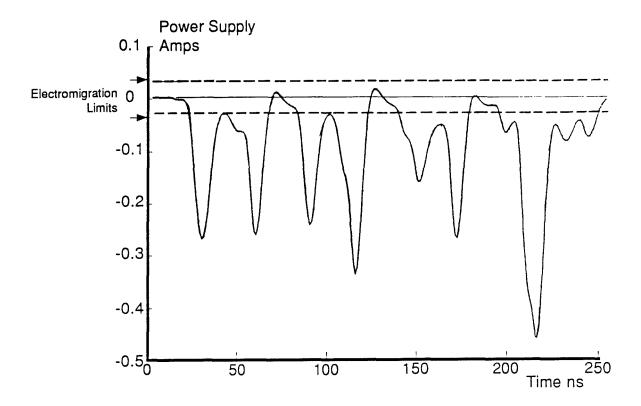

| Fig 5.7(a) | Vdd Supply Current for Processor Slice (20MHz Operation) |  |  |

| Fig 5.7(b) | Vdd Supply Current for Processor Slice (40MHz Operation) |  |  |

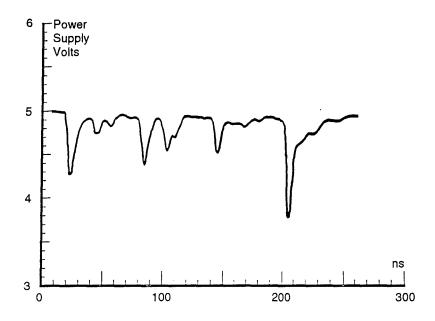

| Fig 5.8    | Vdd Supply Current for Memory Reticle                    |  |  |

# ON THE NATURE AND EFFECT OF POWER DISTRIBUTION NOISE IN CMOS DIGITAL INTEGRATED CIRCUITS

#### **Kevin Kennedy Johnstone**

#### - ABSTRACT-

The thesis reports on the development of a novel simulation method aimed at modelling power distribution noise generated in digital CMOS integrated circuits.

The simulation method has resulted in new information concerning:

- 1. The magnitude and nature of the power distribution noise and its dependence on the performance and electrical characteristics of the packaged integrated circuit. Emphasis is laid on the effects of resistive, capacitative and inductive elements associated with the packaged circuit.

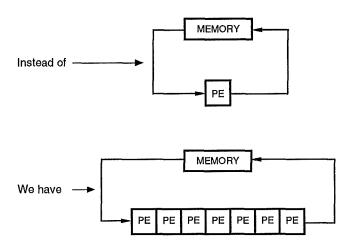

- 2. Power distribution noise associated with a generic systolic array circuit comprising 1,020,000 transistors, of which 510,000 are synchronously active. The circuit is configured as a linear array which, if fabricated using two-micron bulk CMOS technology, would be over eight centimetres long and three millimetres wide. In principle, the array will perform  $1.5 \times 10^{11}$  operations per second.

- 3. Power distribution noise associated with a non-array-based signal processor which, if fabricated in 2-micron bulk CMOS technology, would occupy 6.7 sq.cm. The circuit contains about 900,000 transistors, of which 600,000 are functional and about 300,000 are used for yield enhancement. The processor uses the RADIX-2 algorithm and is designed to achieve 2 X 10<sup>8</sup> floating point operations per second.

- 4. The extent to which power distribution noise limits the level of integration and/or performance of such circuits using standard and non-standard fabrication and packaging technology.

- 5. The extent to which the predicted power distribution noise levels affect circuit susceptibility to transient latch-up and electromigration.

It concludes the nature of CMOS digital integrated circuit power distribution noise and recommends ways in which it may be minimised.

It outlines an approach aimed at mechanising the developed simulation methodology so that the performance of power distribution networks may more routinely be assessed.

Finally, it questions the long term suitability of mainly digital techniques for signal processing.

## **ACKNOWLEDGEMENTS**

I thank Professor John Butcher of the Microelectronics Centre at Middlesex Polytechnic for affording me the research fellowship and for his able guidance throughout my research programme.

I thank Andrew Stewart, formerly of Plessey Research (Caswell) Limited, for a concise description of his signal processing architecture and for his helpful assistance in general.

I thank Dr. Will Moore of the Department of Engineering Science at the University of Oxford for his advice and support at various stages of the programme.

I thank Dick Pearson of Texas Instruments Limited for his expert preparation of all illustrations and text.

This research programme was funded by the UK Alvey Directorate together with Middlesex Polytechnic.

#### INTRODUCTION

#### 1. Research Objectives

The objectives of this research programme are as follows.

- (i) To develop an accurate and flexible method of assessing the degree to which power distribution noise is generated in CMOS digital integrated circuits.

- (ii) To determine the magnitude of the power distribution noise and its dependence on the performance and electrical characteristics of the packaged integrated circuit.

- (iii) To assess the extent to which power distribution noise limits the achievable level of synchronous circuit activity for CMOS digital integrated circuits.

#### 2. Scope of Thesis

The programme is concerned with an array-based and a non-array-based digital signal processor. More specifically, it is concerned with a generic bit-level systolic array processor and a non-array-based 32-bit floating-point processor conforming to IEEE standard 754. For reasons given below, it is assumed that each is fabricated with two-micron bulk CMOS technology.

These architectures were chosen for the following reasons.

The systolic array has a simple structure which is extremely regular and is often cited as a good architecture [a01], [a02] with which to develop yield-enhanced circuits. In addition, its simple, regular structure is amenable to the development of a noise modelling technique.

The chosen non-array-based architecture is a prototype for a commercially available yield-enhanced integrated circuit. At the time of defining the research programme, this prototype was the only such fault-tolerant circuit in Europe. It represented the highest level of monolithic integration for a digital signal processing circuit.

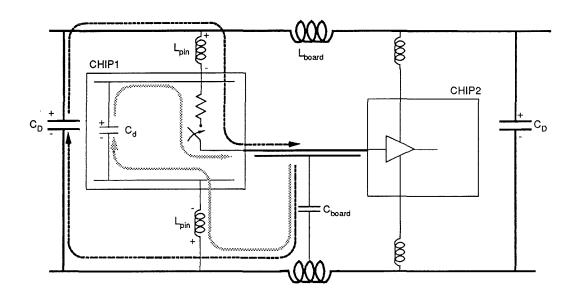

The analysis is concerned with power distribution noise associated with core circuitry and not with peripheral I/O drivers.

The analysis will not be concerned with the effects of resistive, capacitative or inductive elements which are outside the integrated circuit package. An excellent treatment of this problem has been undertaken recently by Keenan [a03].

This analysis will focus on the effects of resistive, capacitative and inductive elements associated with the circuit and with the package itself. In short, it will undertake an

analysis of the primary source of power distribution noise associated with digital computing systems.

Fabrication-related transistor and metallisation parameters were derived from manufacturing data. Accurate data relating only to two-micron bulk CMOS were available.

#### 3. Thesis Structure

Chapter one introduces the technological issues which limit the electrical performance of packaged integrated circuits. The issues addressed are: 1) the electrical characteristics of interconnect and interconnect modelling; 2) clock distribution 3) the electrical characteristics of integrated circuit packages; and 4) power distribution noise.

The objective of chapter two is to review all published analyses of power distribution noise associated with CMOS digital integrated circuits.

Of these analyses [c01], [c02] and [c03] are concerned with simultaneous output driver switching, leaving only [c04], [c05] and [c06] which undertake detailed analyses of power distribution noise associated with core sections of CMOS integrated circuits.

The objective of chapter three is to introduce array-based architectures, systolic architectures in particular, as used to address compute-bound problem solving in digital signal processing and to describe the development of a simulation model used to predict power distribution noise for such highly synchronous architectures.

Chapter three then describes the nature of the power distribution noise and how the model predictions were used to assess the extent to which power distribution technology limits the performance and levels of integration of such circuits. The model is able to predict the power distribution noise associated with a generic systolic array circuit comprising 1,020,000 devices, of which 510,000 are synchronously active. The circuit is configured as a linear array which, if fabricated using two-micron bulk CMOS technology, would be over eight centimetres long and three millimetres wide.

Chapter four is an account of how the simulation methodology, developed in chapter three, was applied to the non-array-based signal processor referred to above. In contrast to the analysis of chapter three, it is not justifiable in the case of a non-array-based architecture to assume that any single circuit dominates the power distribution noise, thus necessitating a detailed analysis of each circuit sub-block and the conditions applicable to each operational mode. In two-micron bulk CMOS technology, the circuit would occupy about 6.7 sq.cm. It contains about 900,000 transistors of which about 600,000 are functional and 300,000 are used for yield enhancement.

Chapter five has two sections. The first is concerned with latch-up and the second with electromigration. This chapter presents an analysis of the extent to which the power distribution noise levels, predicted in chapters three and four, affect circuit

susceptibility to transient latch-up and electromigration.

#### 4. Statement of Originality

The programme of work outlined in this thesis was inspired by Itoh, Nakagawa, Sakui, Horiguchi and Ogura [c05] and by Lea [a04].

As far as can be ascertained, it has resulted in: 1) a novel simulation method which has proven useful in the assessment of power distribution noise; and 2) new information concerning the nature of power distribution noise and the extent to which it may limit the achievable level of synchronous circuit activity for CMOS digital integrated circuits.

## TECHNOLOGICAL CONSTRAINTS

#### 1.1 Introduction

The objective of this chapter is to introduce the technological issues which have constrained, and those that may constrain, the level of synchronous activity associated with CMOS digital integrated circuits.

The issues addressed in this chapter are the electrical characteristics of interconnect, interconnect modelling, clock distribution, the electrical characteristics of integrated circuit packages and power distribution noise.

The integrated circuit, invented by Texas Instruments in 1959 [b01], [b02], has undergone continuous development aimed at increasing integration levels. This has been realised through regular reductions in transistor dimensions, increases in the circuit area and by improvements in circuit packaging [b03], [b04]. Between 1959 and 1983 transistor dimensions were reduced by eleven percent per year on average and circuit area was increased by nineteen percent per year on average [b05]. These two factors combine to yield an increase in the level of integration in excess of fifty-fold per decade.

Though desirable, this high growth rate has not been sustained in recent years and may fast be approaching a technologically-constrained limit. What are the technological issues which determine the maximum level of circuit integration? The question may be put more precisely: what are the issues which determine the maximum level of *synchronous circuit activity?*

Throughout the development of the integrated circuit, the main factor that has determined the achievable level of circuit integration is fabrication integrity. Reductions in transistor dimensions and increases in circuit area each have increased circuit susceptibility to process and packaging imperfections leading to a lower proportion of functional devices or lower manufacturing yield.

The maximum level of synchronous circuit activity clearly is dependent on transistor size, circuit size and packaging technology. Until recently, the sole metric which has influenced their choice is manufacturing yield. As manufacturing yield improves, allowing the manufacture of circuits with many more devices, circuit-level electrical performance may emerge as an additional factor which must be analysed if the full potential of the integrated circuit is to be realised.

#### 1.2 Interconnect Modelling

#### 1.2.1 Interconnect scaling

Interconnect elements no longer may be considered to have negligible impact on the performance of integrated circuits. With reductions in circuit feature size and

increases in circuit dimensions, parasitic interconnect capacitance and resistance are increased to effect delays which are comparable with gate delays.

Gate delays are decreased because transistor gate, gate-drain overlap and sourcedrain areas are reduced. Interconnect capacitance is increased as a consequence of an increase in circuit size. This typically more than compensates the reduction in interconnect capacitance per unit length as a result of reduced interconnect track widths.

Interconnect resistance is increased as a result of an increase in circuit size and as a result of reduced cross-sectional area. Interconnect resistivity is independent of cross-sectional area unless this is reduced to a level which is similar to the mean-free-path of the electron. For aluminium, mean-free-paths are less than 100nm and consequently it is reasonable to assume no dependence.

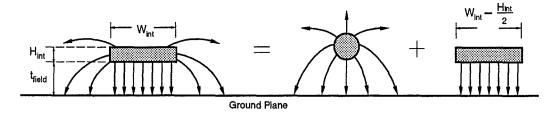

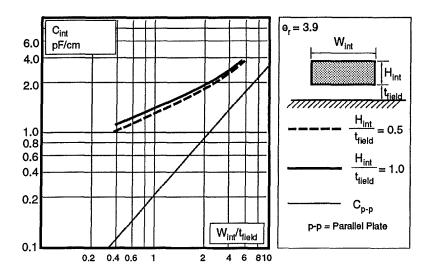

Interconnect capacitance can be modelled by an area term and a periphery term. As shown in Figure 1.1, interconnect capacitance can be modelled by a combination of a parallel plate capacitor of width  $W_{int}$  and a cylindrical wire of diameter  $H_{int}$  [b06]. In Figure 1.2,  $C_{int}$  is shown plotted as a function of  $W_{int}/t_{field}$  for two  $H_{int}/t_{field}$  ratios where  $t_{field}$  is the transistor field oxide thickness. It can be seen that  $C_{int}$  approaches an asymptote of 1pF/cm when  $W_{int} \approx t_{field} \approx H_{int}$ . This is due to peripheral or "fringe" effects.

Fig 1.1 Interconnect Capacitance - Area & Periphery Terms

A third capacitance term is that associated with coupling to neighbouring interconnect lines. This coupling term has the undesirable effects of degrading switching speed and enhancing circuit noise thereby degrading significantly circuit performance.

It is clear, from Figure 1.2, that as circuit features are made smaller and circuit sizes are increased, area effects increasingly are dominated by periphery and coupling effects. The problem of analysis therefore grows from one of capacitance per unit length to capacitance per unit area and capacitance per unit volume.

Multi-dimensional modelling aimed at accurately predicting interconnect capacitance has been reported extensively [b07], [b08], [b09].

#### 1.2.2 Distributed RC Lines

The response of a *lumped* RC network to a step potential is

$$V(t) = 1 - \exp(-t/RC)$$

Fig 1.2 Interconnect Capacitance vs Interconnect Width/Oxide Thickness

The time-domain solution of a "distributed" RC network does not exist in closed form. Solutions valid for t<<RC and t>>RC can be obtained by using an approximate expansion for the hyperbolic cosine function associated with the frequency-domain solution.

$$cosh(x) = exp(x)/2$$

for x>>1

and

$cosh(x) = 1+x^2/2! + x^3/4!$  for x<<1

The approximation for large x thus is appropriate for high frequency signal components; for small x, it is appropriate for low frequency signal components. Signal transitions are high frequency components while steady-state values are low frequency.

Such time-domain and frequency-domain solutions are difficult to use, however, and it is known that a distributed RC line can be approximated by a lumped resistor and capacitor network.

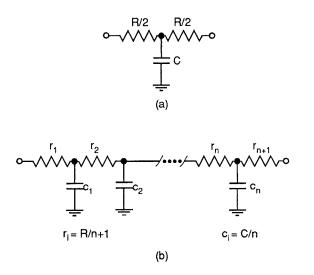

This approximation lends itself well to computer-aided circuit simulation and the commonly adopted resistor/capacitor configurations are shown in Figure 1.3. The question most often raised in connection with lumped element RC approximation is: "how many sections are needed accurately to model the performance of the distributed line?".

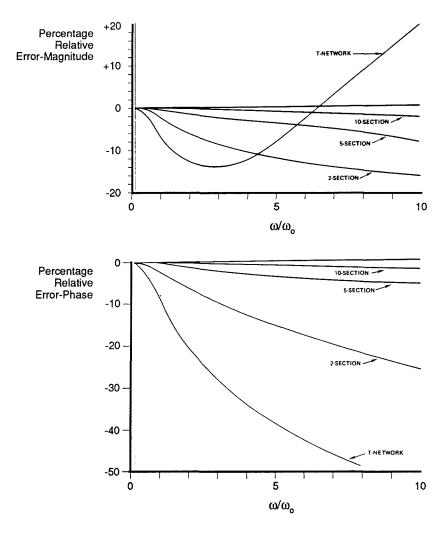

Antinone and Brown [b10] set about answering this question by undertaking frequency-domain simulations for a T-network and a 2-, 5- and 10-section ladder network and comparing them with exact mathematical analyses. Their results are shown in Figure 1.4. The authors conclude that the number of lumped elements should be chosen so that the time constant of each  $(r_n.c_n)$  is one-tenth the time constant associated with the interconnect section being studied.

Fig 1.3 T-network & Ladder Network distributed RC models

Fig 1.4 Error of Simulated Results Relative to Theoretical as a Function of Frequency

#### 1.2.3 Transmission Lines

Longer interconnect lines and higher clock frequencies associated with larger integrated circuits constituted by smaller, and consequently faster, devices ultimately will result in clock transition times which are comparable with interconnect delay. At this stage, inductance becomes a significant electrical characteristic of integrated circuit interconnections and therefore introduces the need for transmission line modelling.

Fig 1.5 Inductive & Capacitive Discontinuities

To obtain accurate inter-circuit delay and noise estimates, bond wires, package parasitics and circuit board interconnections are modelled as transmission lines. At the circuit board level, signal reflections can be generated at capacitative and inductive discontinuities due to interconnect lines, connectors, package pins, vias and corners associated with board wiring.

As an example of such phenomena, Figure 1.5 illustrates signal reflections associated with a capacitative and an inductive discontinuity. The transmission line is driven by a signal generator with source resistance  $R_{\rm S}\!\!=\!\!Z_{\rm O}$  and the reflected signal is observed at the source. It is assumed that the line is infinitely long so that all reflections are due to the discontinuity.

Immediately after the signal reaches the discontinuity, the capacitor has low impedance and shorts the line. Later its impedance is restored and the voltage disturbance decays with a time constant  $Z_0C/2$ .

The inductor, on the other hand, has high impedance immediately after the signal reaches the discontinuity and the voltage step doubles. Later, as current increases, its impedance falls and the voltage disturbance decays with a time constant of  $L/2Z_0$ .

In the second set of signals, shown in Figure 1.5, it is assumed that the input step has a rise time which is larger than the discontinuity time constants. Then there is insufficient time for the disturbances to reach their theoretical maxima.

| Rise Time<br>t <sub>r</sub> (ps) | Critical Line Length<br>lcrit=vt/2.5 (cm) |  |

|----------------------------------|-------------------------------------------|--|

| 50                               | 0.3                                       |  |

| 100                              | 0.6                                       |  |

| 250                              | 1.5                                       |  |

| 500                              | 3.0                                       |  |

| 750                              | 4.5                                       |  |

| 1000                             | 6.0                                       |  |

Fig 1.6 Critical Transmission Line Lengths

At present, CMOS integrated circuits do not exhibit transmission line effects; they are insufficiently large or fast. How large and fast need they be? Transmission line behaviour becomes significant when the rise time,  $t_{\rm r}$ , of a signal becomes comparable with, or less than, interconnect delay,  $t_{\rm int}$ .

It is assumed that transmission line phenomena become "significant" when interconnect delay is comparable with, or less than, one quarter period of the dominant Fourier component associated with the clock signal. When this is true, it can be shown that  $tr < 2.5t_{int}$ . Interconnect lengths corresponding to  $tr = 2.5t_{int}$ , so-called critical transmission line lengths, are listed for CMOS technology in Figure 1.6.

Fig 1.7 Unterminated Transmission Line driven by a Source Resistance  $R_s$

The relationship is complicated further by a dependence on the ratio of signal source resistance Rs to the characteristic impedance of the line  $Z_0$ . If the transmission line of Figure 1.7 is modelled as a lumped capacitor, the rise time of the resulting RC network can be expressed as

$$t_r = 2.3R_sC = 2.3R_scl$$

where 'c' is the capacitance per unit length and 'l' is the transmission line length. The delay of the line is expressed as  $t_{int}$  = l/v where 'v' is the signal velocity.

Transmission line phenomena would be negligible if the round-trip delay of the line

were much less than the rise time ( $2t_{int} \ll t_r$ ). For this to be true

$$1/v \ll R_s cl \Rightarrow 1/v.c \ll R_s$$

It is thus concluded that

$$Z_0 = 1/vc \Rightarrow Zo \ll R_s$$

An additional requirement on the relationship for transmission line phenomena is that the signal source resistance should be much less than the characteristic impedance of the line.

$$V_{in} \stackrel{\textstyle \mathsf{R/n}}{} \stackrel{\textstyle \mathsf{L/n}}{} \stackrel{\textstyle \mathsf{R/n}}{} \stackrel{\textstyle \mathsf{L/n}}{} \stackrel{\textstyle \mathsf{L$$

Fig 1.8 Lossy Transmission Line Model

The above analysis applies to loss-less transmission lines. Integrated circuit interconnects, usually of aluminium, have significant resistance and should be modelled as lossy transmission lines. Resistance introduces signal attenuation and it can be shown that for a lossy transmission line of length 'l', the voltage transfer function can be expressed as

$$T = \exp(-R/2Z_0)$$

where R is the total line resistance and  $Z_0$  its characteristic impedance.

Figure 1.8 illustrates an approximate model for a lossy transmission line. This can be used easily in circuit simulators. For this case,

$$Z_0 = \sqrt{(L/C)}$$

; and,  $t_{int} = \sqrt{(LC)}$

where R, C and L are the total resistance, capacitance and inductance of the line.

Transmission line phenomena for integrated circuit interconnect are complicated further by the "slow wave" effect [b11], [b12]. The explanation of this effect lies in the fact that the semiconductor behaves as a conductor for capacitative effects and as an insulator for inductive effects thereby "distorting" magnetic and electric fields associated with the interconnect.

Integrated circuit transmission line effects have been analysed and reported on extensively [b13], [b14], [b15]. These analyses have been embraced in the development of simulators such as MCLINES, which can be used to predict accurately capacitance and inductance values for the equivalent circuit of Figure 1.8.

Fig 1.9 Clock Distribution Tuning

Clock distribution is, by implication, of major concern in the design of highly synchronous integrated circuits. It is clear that, if the improved performance associated with smaller devices is to be exploited, then clock periods will be shortened. Similarly, it is clear that as circuit sizes increase, then it will be necessary to distribute the clock further from its source along lossy transmission lines [b16], [b17].

#### 1.3.1 Clock Skew

Clock skew manifests itself in two forms. The first is if two circuits, governed by the same clock, are not equidistant from the clock driver. They consequently have unequal interconnect loading and receive the clock at different times. The second is when process variations have resulted in unequal gate and interconnect delays. For each, the effect is the same: to reduce the degree of synchronous activity in the circuit.

Clearly, as clock periods are reduced, circuits will exhibit increased susceptibility to clock skew. For this reason, it is useful to think of clock skew, expressed as a fraction of the clock period, as a measure of the effectiveness of the clock distribution scheme.

Clock skew is not often controllable by design. If it is, then it can be used to effect an improvement in circuit performance. This is referred to as "tuning" the clock signal or the clock distribution network. For example, if the delays associated with pipeline stages are unequal, circuit performance may be optimised either by retarding the data capture clock for slower pipeline stages or by advancing it for faster stages. This technique is illustrated in Figure 1.9.

Though useful, it must be stressed that the intentional introduction of clock skew necessitates precise skew control, a task more exacting and generally less robust than skew minimisation through advanced distribution schemes. Two common examples of such schemes are locally synchronous and H-tree clock distribution.

#### 1.3.2 Locally Synchronous Distribution

In this scheme the circuit, or system, is partitioned into synchronous islands each with its own independent clock. This technique avoids the distribution of a single global clock which inevitably will lead to unacceptable clock skew and compromised performance.

Once the circuit, or system, is divided into locally synchronous regions, clock skew problems effectively are transferred to the inter-region communication mechanism [b18], [b19], [b20]. There exist two common communication mechanisms: 1) asynchronously using a self-timed discipline; and 2) synchronously using a global clock of lower frequency than the local clocks.

A self-timed discipline is one which is made up of speed-independent circuits which communicate via a set of asynchronous protocols [b18], [b19]. The system changes state only when all circuits signal completion, thereby eliminating the need for a global clock and thus, by definition, the clock skew problem disappears.

Another advantage of self-timed systems is that, unlike synchronous systems, performance is not determined by the worst-case signal delay. In a self-timed system, a computational step is initiated after its sequential predecessors have completed their computational steps. The total delay is the aggregate delay of the computational steps and as such it reflects the average delay instead of the worst-case delay [b20].

If the worst-case path is activated only rarely, a self-timed system will perform better than a synchronous one but at the cost of the extra logic required for communication.

In the case of the second mechanism, the locally synchronous regions use a relatively high frequency clock and the global communication is achieved with a much lower frequency bus. In practice, the bus width is determined by a combination of the system requirements and the maximum supportable global clock frequency.

A possible complication of this communication mechanism is that of metastability introduced by clock skew between local and global clocks [b21], [b22]. This can be avoided through the use of phase-locked loop circuits to adjust dynamically the relative phase of the clocks [b23].

Fig 1.10 Multiple Driver Distribution Scheme

Fig 1.11 Successively Higher Gain Driver Distribution Scheme

The mechanism is flexible in the sense that it may be extended to include a hierarchy of clock frequencies appropriate for large circuits containing small regions of relatively high performance circuitry. This technique has been adopted by Lea and Coleman [b24] in the development of their associative processing architecture.

## 1.3.3 The H-tree Distribution

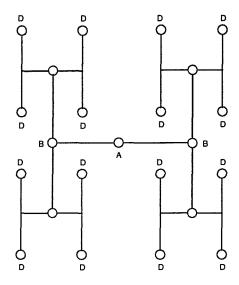

Figure 1.10 shows a regular clock distribution scheme used to reduce clock skew due to interconnect. In this scheme, the idea is to use identical clock drivers with equal loads. The principal cause of clock skew is then that of unequal driver delay due to process-related parametric spread. If interconnect delay is relatively insignificant in comparison with delay mismatch, skew can be further reduced by replacing the multiple buffer structure of Figure 1.10 with that of Figure 1.11 in which the tree branches are driven by a cascade of a successively higher gain drivers.

In order that clock skew be minimised, the clock should be distributed in such a way that the clock is electrically equidistant from all functional blocks it serves. Clock signals will be delayed equally on arrival at the interface to the functional block as in the case of the locally synchronous system. Intra-block clock skew will be dependent on block size which therefore can be chosen to be as large as the application can sustain.

The clock distribution scheme shown in the Figure 1.12 [b25] adopts the above ideas by repeating recursively an H-shaped structure. Clearly, this H-tree scheme can be easily extended to a distribution system in which phase-locked loop circuits have been included to minimise process-related variations in regional clock driver delays. This distribution scheme offers minimal clock skew and may be applied to systems ranging from circuit boards through to sub-circuits of an integrated circuit.

Fig 1.12 H-tree Clock Distribution Scheme

## 1.4 Packaging Technology

Packaging is required to supply integrated circuits with an electrical interface to the outside world, to remove heat generated by the circuit and to provide the circuit with physical support and environmental protection.

Currently, as much as 50% of computer system delay is attributable to packaging.. This figure has been estimated to increase to 80% by the end of the decade [b26].

In order that system performance be optimised, it will be necessary to ensure: 1) that packages contain larger circuits; and 2), that they are grouped more densely on circuit boards.

It is for these reasons that increased importance must be placed on the electrical and thermal characteristics of integrated circuit packages.

#### 1.4.1 The Dual-in-Line Package

The dual-in-line package derives its name from its pin configuration and remains the most common form of integrated circuit packaging. It is usual to find through-hole board mounting technology used in combination with this form of packaging.

Dual-in-line packaging is formed by bonding the integrated circuit to a bond lead frame. Wire bonds are made subsequently to provide electrical connections from the circuit to the bond leads and the whole device is encapsulated either in ceramic or, more commonly, in plastic.

Dual-in-line packages are inserted through the holes of a circuit board and, to effect permanent electrical contact, the entire bottom surface of the board is dipped in a solder which adheres only to the metal pins, the copper-plated walls of the holes and the contact areas surrounding the holes.

Through-hole mounting provides robust mechanical support to the circuit and offers high resistance to thermal stress. In combination with dual-in-line packaging, however, it does not provide good packing density. Inherently, the pin configuration of dual-in-line packages gives rise to "pin-bound packages" and through-hole mounting makes inefficient use of board space since it occupies both sides of the circuit board.

The above factors result in relatively lengthy board-level interconnections which, combined with dual-in-line package parasitics, are likely to degrade system performance [b27], [b28].

#### 1.4.2 The Pin Grid Array

An alternative to the dual-in-line package is the pin grid array. Unlike the dual-in-line package, the pin grid array features bond leads on its entire bottom surface. This configuration offers obvious benefits over the dual-in-line package and pin-outs of over 300 are practical with pin grid arrays.

Pin grid arrays are available in two forms: cavity-up and cavity-down depending on whether the pins and circuit are fixed on the same or opposite sides of the, usually square, package. The advantage of the cavity-up form is that a heat sink may be attached to the reverse side of the package while the advantage of cavity-down is that one entire side may be occupied by pins.

To support a high pin-out, pin grid arrays require multilayer ceramic, usually alumina, substrates. This requirement results in pin grid arrays having two undesirable features. They have high bond lead parasitics because of the high dielectric constant of alumina, and they are subject to mechanical stress at the circuit board interface. On the positive side, ceramics do exhibit high thermal conductivity and provide good hermiticity.

As an alternative to multilayer ceramic substrates, pin grid arrays may be made up of circuit board epoxy fibreglass. Although these packages have reduced thermal mismatch and lower bond lead parasitics, their thermal conductance and hermeticity is relatively poor.

#### 1.4.3 Surface Mounting

Surface mounting is a more advanced technology in which a circuit package is bonded to pads on the surface of a circuit board. Surface mount technology provides for smaller packaged devices which may be connected to both sides of the circuit board. As a result of these provisions, system performance is enhanced through reduced package and board parasitics.

From a manufacturing viewpoint, surface mounting is inherently easier than throughhole mounting though it does restrict test visibility of package pins and shows increased susceptibility to thermal stress through mechanically weaker connections.

Electrical connections between circuit pads and package are realised most often with wire bonding. Tape-automated bonding and flip-chip mounting are alternatives. The benefits and potential problems associated with each technique are addressed in the following sub-sections.

#### 1.4.4 Wire Bonding

Using this technique, the integrated circuit is fixed to a lead frame with an adhesive which provides low thermal resistance. Aluminium wires then are individually attached so as to connect all circuit pads to the lead frame. The wire material is aluminium because of its low electrical resistance and malleability.

Although this technique so far has proved both cost-effective and reliable, it may not continue to be so as packages are required to integrate larger circuits with greater I/O requirements. Since the wires are individually bonded, there may not be adequate throughput in production.

Aside from these issues, typical bond wires exhibit a parasitic inductance of about 5nH. Will this property remain an acceptable parasitic as the levels of integration and synchronous circuit activity are increased?

#### 1.4.5 Tape-automated Bonding

Tape-automated bonding involves placing solder bumps on diced circuits which subsequently are aligned with copper leads fabricated in multilayer polyimide tapes. The bond is created by reflowing the solder and the tape is fed to automatic test and assembly machines which may place the device directly on to a circuit board.

This technique offers relatively high throughput since all bond connections are created simultaneously. In comparison with wire bonding, tape-automated bond lead separation is low due to the rigid supportive structure of the polyimide film. Tape-automated bonding requires relatively short leads and consequently exhibits reduced parasitic effects. The minimum bond lead pitch achievable with tape-automated bonding is about 0.08mm. The minimum pitch for wire bonding is about twice as much.

The disadvantage of tape-automated bonding is that the embedded bond lead patterns and pattern sizes are normally different for different circuits. This technique consequently is expensive and normally is used only for high-volume circuits.

A logical extension of tape-automated bonding is to make bond lead connections over the whole surface of the integrated circuit. This technique is known as area tapeautomated bonding and its advantages are clear. Signals are no longer constrained to be at the periphery of the circuit.

| Component                      | Capacitance<br>(pF) | Inductance<br>(nH) |

|--------------------------------|---------------------|--------------------|

| 68 pin plastic DIP ‡           | 4                   | 35                 |

| 68 pin ceramic DIP#            | 7                   | 20                 |

| 68 pin SMT chip carrier lead ‡ | 2                   | 7                  |

| 68 pin PGA pin <sup>‡‡</sup>   | 2                   | 7                  |

| 256 pin PGA pin#               | 5                   | 15                 |

| Wire Bond                      | 1                   | 1                  |

| Solder Bump                    | 0.5                 | 0.1                |

<sup>‡</sup> No ground plane; capacitance is dominated by wire-to-wire component.

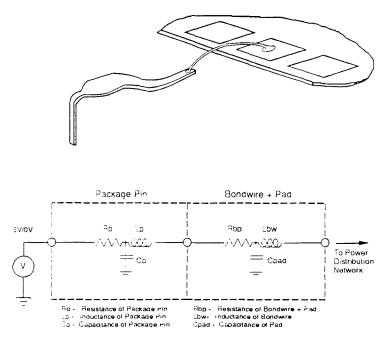

Fig 1.13 Package Electrical Parasitics

Direct tape-automated bonding clearly is more suited than wire bonding, to large circuits with higher I/O requirements. Prototype direct tape-automated bonding on circuit boards has been developed to support more than 500 leads per circuit [b29]. Thermal mismatch between circuit and circuit board remains a problem for this technique which can but worsen as circuits become larger.

#### 1.4.6 "Flip-chip" Mounting

Further reductions in bond lead length can be realised by placing solder bumps on the circuit, aligning them with contact pads on the package substrate, and reflowing the solder to create the bond. This method provides electrical connections with parasitic inductances of lower than 1nH and capacitances of lower than 1pF. In addition, the technique clearly offers the possibility of non-peripheral bonding. One obstacle facing this technique is associated with its resultant high thermal resistance. Unless a thermal contact is made to the back of the circuit, the thermal path from the circuit to the package is limited to the solder bumps.

Another obstacle is that of thermal mismatch between the circuit and the package substrate. This will lead inevitably to mechanical strain at each of the solder bumps and to unacceptably high failure rates. In large circuits especially, this strain is minimised by concentrating the bumps at the centre of the circuit [b30]. This constraint has the obvious effect that non-peripheral bonding would, in practice, be restricted to the centre of the circuit.

A summary of electrical parasitics associated with the above packaging techniques is given in Figure 1.13.

#### 1.4.7 Thermal Properties

As integrated circuits become larger and operate at higher frequencies, they are bound to generate more heat. Since almost all failure mechanisms are enhanced by

<sup>‡‡</sup> With ground plane; capacitance and inductance are determined by the distance between the lead frame and the ground plane, and the lead length.

higher temperatures, increasingly large portions of this heat must be removed if future packaged circuits are to have acceptable reliability. In order to meet commercial reliability requirements, circuits typically operate in the temperature range 0°C to 85°C and are stored in the range -55°C to 125°C.

In the case of plastic dual-in-line packages, there are three major thermal paths from the circuit to the ambient: from integrated circuit to package via the circuit bond material, from the circuit to the package pins via the wire bonds and bond lead frame and from circuit to ambient via the package plastic moulding. The second of these paths is often assisted by a metal sheet placed under the circuit.

The thermal resistance of a 40-pin dual-in-line package may be as low as 38°C/W using natural convection and 25°C/W with forced air convection. Given the desired temperature range for reliable operation, a dual-in-line package may dissipate up to 2W with natural convection and up to 3W with forced air convection.

Pin grid arrays, unlike dual-in-line packages, are always made up of a multilayer ceramic such as alumina or beryllia with a hermetically-sealed air cavity above. As was discussed in 1.4.2, cavity-down pin grid arrays may have heat sinks attached to one side. In these packages, the primary thermal path is via the circuit bond material, the ceramic substrate and the heat sink.

In the case of flip-chip mounting, the major thermal path from the circuit to the package substrate is via the solder balls and any attached heat sink. The scheme was developed by IBM for their 3081 processor unit [b31]. Heat is transferred from the circuit to pistons which, in turn, conduct it to a water-cooled plate. In addition, the circuit cavity is helium-filled to assist the cooling process. The resultant thermal resistance of the package is  $11^{\circ}$ C/W per integrated circuit site. Since the piston diameter is the same as the circuit length, circuit sites may be closely packed thereby minimising inter-circuit electrical parasitics.

The resultant package provides an environment in which densely packed integrated circuits may dissipate up to 4W of power and raise their junction temperatures only 44°C above that of the cooling water [b32].

#### 1.5 Power Distribution

#### 1.5.1 Simultaneous Switching Noise

Given that integrated circuit technology is being driven to facilitate larger circuits constituted by smaller devices operating at higher frequencies, it is important to consider the implications, if any, for necessarily global signals such as the circuit power supply.

It has been stated, in section 1.2 on interconnect modelling, that larger circuits will possess higher interconnect capacitance. In addition it is clear that, with increased switching speed and more densely packed devices, the rate of change of current (di/dt) needed to charge and discharge these larger capacitors similarly will be higher.

It is conceivable that di/dt will increase to levels such that the packaging- and interconnect-related inductive parasitics, discussed in sections 1.2 and 1.4, introduce power supply level fluctuations which significantly affect circuit performance. Such fluctuations are described by Faraday's Law written as

$$EMF = V_{disturb} = -Ldi/dt$$

At present, di/dt induced power distribution noise, is associated only with simultaneously switching circuit output drivers. As circuits are made larger and faster, or more synchronously active, power distribution noise associated with "core" circuitry may become equally important.

The complementary nature of digital CMOS circuitry is such that it is driven half passive. During a given cycle, the active devices will remove current from the positive supply and add current to the negative supply. This results in reduced power supply voltage integrity as the board power plane supplies current via the pin inductor.

Since the passive circuitry is connected to the relatively low inductance power supply

Fig 1.14 Simplified Model of a CMOS Circuit, Package & Power Supply

distribution network via the on-resistance of the passive transistors, charge-sharing between active and passive circuits tends to compensate the demands of the active circuitry and thereby reduces the reduction in supply integrity.

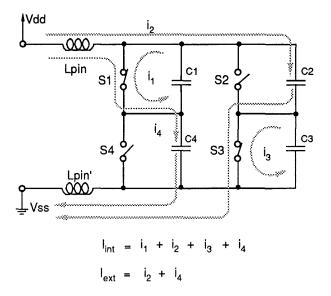

It must be noted that the above effect acts only partially to compensate the current demands of active circuitry. Current always will flow in from and out to the external supply via the pin inductor. This fact can be explained with reference to the simplified electrical representation of active CMOS circuitry shown in Figure 1.14.

It is assumed that initially switches S1 and S3 are open and switches S2 and S4 are closed. In this state, capacitors C1 and C3 have a potential difference across them equal to the circuit power supply while capacitors C2 and C4 are discharged. It is next assumed that switches S1 and S3 close and S2 and S4 open. In this state, charge

redistribution associated with capacitors C1 and C3 will happen independently of the external supply whereas current will flow from the external positive supply via the pin inductor to capacitors C2 and C4. Similarly, current will flow from capacitors C2 and C4 to the external negative supply.

Even if, as in this simplified case, currents  $i_1$  and  $i_2$  exactly match  $i_3$  and  $i_4$ ,  $i_3$  and  $i_4$  will flow via the external pin inductor. In practical CMOS circuits, switches S1/S2 and S3/S4 do not precisely complement each other and the associated currents are seldom equal.

#### 1.5.2 Noise Reduction

In section 1.2 it was established that if the signal source resistance  $R_{\rm s}$  is significantly greater than the characteristic impedance of a transmission line, then transmission line phenomena become negligible. It therefore is reasonable to conclude that simultaneous switching noise will create minimum disturbance if the characteristic impedance of the power distribution network is kept to a minimum. Distribution network inductance must therefore be made as small as possible and network capacitance as large as possible.

Network inductance is interconnect- and package-related. Interconnect-related inductance does not, at present, contribute significantly to network inductance. As circuits become larger, however, its significance may increase and could be reduced by using thicker interconnect lines. Package-related inductance such as that associated with package pins and bonding structures may be reduced by increasing their cross-sectional areas, placing them closer to a ground plane and making them shorter. Inductance values for practical packaging options are listed in Figure 1.13 of section 1.4.

Once the separate inductance of individual package pins and bonding structures has been minimised, their effective inductance may be reduced further by placing as many as possible around the circuit thereby to provide parallel power supply current paths to and from the circuit and consequently to reduce absolute di/dt levels. Simultaneous switching noise is reduced.

The above technique has the added advantage of allowing isolation of especially noisy circuitry from relatively quiet high-precision circuitry.

In general, the effective inductance of the circuit power distribution network is proportional to the ground loop area. This may be kept small by forming a power circle around the circuit which then is multiply-bonded to the circuit. Ground loop area is small and therefore so is the effective inductance.

Network capacitance may be increased simply by connecting so-called decoupling capacitors directly to the circuit. If the capacitors are distributed evenly on the network, its characteristic impedance and consequent potential drop will appear to be reduced. A practical realisation of such decoupling techniques developed by IBM is reviewed in the following chapter.

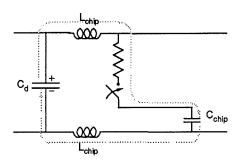

It is important to point out that network decoupling capacitors are ineffective at

reducing noise associated with simultaneously switching output drivers. The "decoupling" path, shown in Figure 1.15, is contained within the circuit in the sense that a portion of the necessary supply current is provided to the decoupling capacitor by inactive circuitry via a low inductance path.

Fig 1.15 On-chip & Off-chip Supply Decoupling Paths

In the case of the output drivers, the path is not contained within the circuit. The system ground which is external to the circuit is connected to the circuit ground via the power supply pins. As can be seen from Figure 1.15, the ground loop is closed by a relatively high package pin inductance. A significant potential drop is developed across this inductor and as the output drives low and high the circuit supply will oscillate.

Network decoupling is useful only on the distribution network which serves "core" circuitry. For the reasons given, it is good policy to isolate core power supply from output driver supply.

Output buffers are often designed with more than adequate gain margin. Thus their contribution to power distribution noise is more than is necessary. It is possible to design output buffers whose gain is controllable so that switching speeds may be

reduced as much as the application will allow. Chapter two will discuss such di/dt-controlled output buffers and their effect on circuit performance overall.

#### 1.6 Conclusions

It is clear that each of the issues addressed above will increasingly impact the level of synchronous activity which can be achieved with digital CMOS integrated circuitry.

To what extent will they impact the level of synchronous activity?

The development of an answer to the above question, for the case of power distribution noise, forms the basis of this research programme.

The precise objectives of the programme are reiterated:

- (i) To develop an accurate and flexible method of assessing the degree to which power distribution noise is generated in CMOS digital integrated circuits.

- (ii) To determine the nature of the power distribution noise and its effect on the performance and electrical characteristics of the packaged integrated circuit.

- (iii) To assess the extent to which power distribution noise limits the achievable level of synchronous circuit activity for CMOS digital integrated circuits.

Aside from a general understanding of the cause of power distribution noise, little is known of its nature or of the extent to which it is present in CMOS digital integrated circuits. More important, little is known of the extent to which power distribution noise may limit the performance of such circuits.

#### 2.1 Introduction

The objective of this chapter is to review all analyses of power distribution noise associated with highly synchronous CMOS digital integrated circuits.

At the time of writing, the sum total of published work on the subject is represented by only six papers. Of these [c01], [c02] and [c03] are concerned with simultaneous output driver switching and [c04], [c05] and [c06] have undertaken detailed analyses of power distribution noise associated with core sections of CMOS digital integrated circuits.

Of the papers concerning core-generated noise, [c04] was published in 1982 from Bell Laboratories, [c05] in 1987 from the Toshiba Corporation and [c06] collaboratively in 1990 from IBM Laboratories and General Technology Division. At the time of writing, these three are the only papers which discuss quantatively core-generated power distribution noise in CMOS digital integrated circuits.

#### 2.2 The Delta-I Simultaneous Switching Problem

Ditlow and Brown [c01] refer to power distribution noise as the "delta-I simultaneous switching problem". They describe the problem from a system viewpoint and develop a Boolean model aimed at identifying potential simultaneous switching hazards. They confine their analysis to the effect of simultaneously switching output drivers.

In developing the model, they consider the definition of a set of input conditions which causes a corresponding set of output drivers to switch simultaneously. Since the output drivers must be preset to a known state, two sets of input conditions are required. Ditlow and Brown address the issue of finding a preset-set input sequence such that the number of simultaneously active outputs is less than a given technology limit. The limit is an assumed upper-bound beyond which the degree of simultaneous switching cannot be supported reliably by the power distribution network.

In order that the two-stage, preset-set, input sequence may be realised, the final form of their "delta-I hazard-flagging model" consists of a single output with twice as many inputs as the original combinational logic network.

The outputs of each model are input to a decision function used to assess the degree of simultaneous unidirectional switching; unidirectional since positive transitions will tend to cancel negative ones. The output of the decision function is then compared with a known technology limit and hence a delta-I switching hazard may be flagged. They conclude that the delta-I simultaneous switching problem can effectively be managed with the Boolean model.

Their analysis is of limited practical use since it is restricted in two ways. These are: (1) only the effect of output driver switching is considered; and, (2) the model rests on the fact that the constraining "technology limit" is known.

#### 2.3 Ground Bounce Control in CMOS Integrated Circuits

Gabara and Thompson [c02] describe a technique for homogenising output driver rise/fall times so that high times, associated with poor processing, are reduced and low times are increased. This has the effect of equalising associated ground noise, or ground bounce, across the process window. They demonstrate the effectiveness of the technique by experiment.

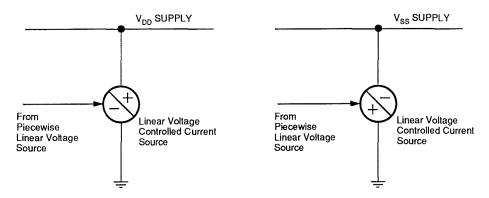

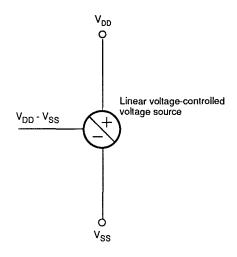

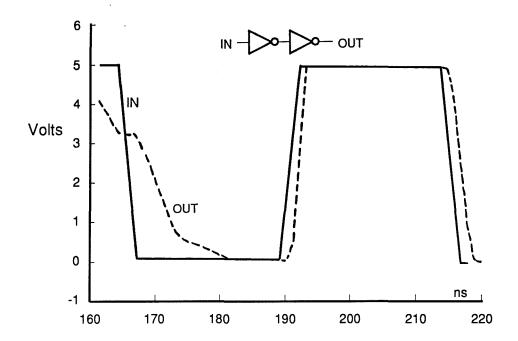

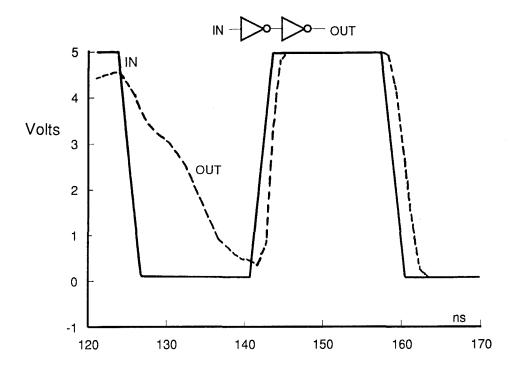

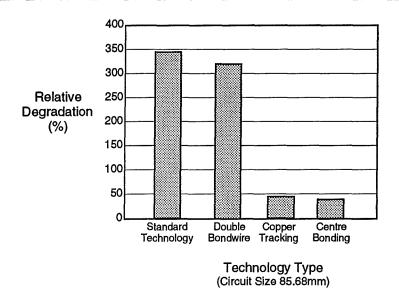

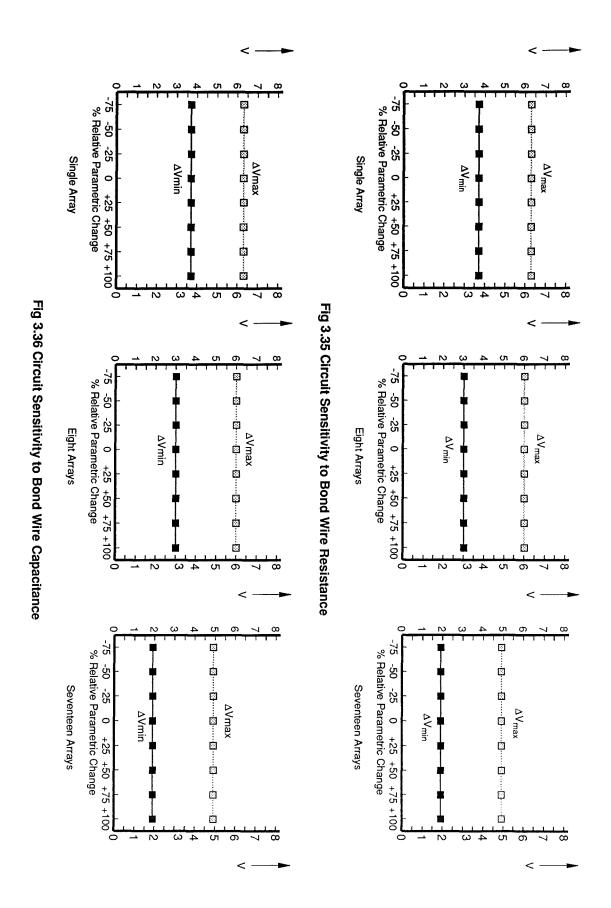

The key feature of their technique is an integrated voltage source used to regulate the charge/discharge rate of the output driver. The voltage source is stable with respect to the process and generates a voltage according to its position within the process window so that the variation in output driver performance is minimised. Ground bounce is equalised with respect to all process variations.