The Sheppard Library Middlesex University The Burroughs London NW4 4BT 020 8411 5852 http://library.mdx.ac.uk

#### **SHORT LOAN COLLECTION**

100

# REFERENCE ONLY Thesis Collection

## BREAKDOWN AND CHARGE TRAPPING

## IN SILICON DIOXIDE FILMS ON SILICON.

Stephanie K. Haywood

A thesis submitted to the C.N.A.A. in partial fulfilment of the requirements for the degree of Doctor of Philosophy.

Middlesex Polytechnic, U.K.

Katholieke Universiteit Leuven, Belgium.

March 1986

| SITE HE          | MIDDLESEX<br>POLYTECHNIC<br>LIERARY |

|------------------|-------------------------------------|

| ACCESSION<br>No. | 8600925                             |

| CLASS<br>No.     | 621 381 73<br>HAY                   |

| SPECIAL V        | Thesis<br>Corlletin                 |

×5955761

|  |  |   | • |

|--|--|---|---|

|  |  |   |   |

|  |  |   |   |

|  |  |   |   |

|  |  |   |   |

|  |  |   |   |

|  |  |   |   |

|  |  |   |   |

|  |  |   |   |

|  |  |   |   |

|  |  |   |   |

|  |  |   |   |

|  |  |   |   |

|  |  |   |   |

|  |  |   |   |

|  |  |   |   |

|  |  | • |   |

|  |  | : |   |

|  |  |   |   |

|  |  |   |   |

|  |  |   |   |

#### **ACKNOWLEDGEMENTS**

The efforts of many people made it possible for the work described here to be carried out and several others assisted with the actual thesis production. I would like to thank everyone who helped for their invaluable contributions. In particular, my thanks to Prof. John Butcher of Middlesex Polytechnic Microelectronics Centre for introducing me to this field, for the opportunity to pursue this research in collaboration with the University of Leuven and for his advice regarding the thesis content and presentation. Thanks also, to my friends and colleagues at Middlesex Polytechnic (especially Moni Deb, Dr. Peter Revell and Dr. Kumar Das) for many stimulating discussions during the time I spent in London. Susan Partridge, Head of the Advanced MOS division at GEC Research Centre in Wembley provided samples and access to equipment in the early days of this work for which I am most grateful.

Special thanks to everyone at ESAT and IMEC in Leuven for helping to make the years I spent there happy and productive. Dr. Roger DeKeersmaecker provided endless scientific advice and support throughout this time. A number of errors were avoided and several improvements made as a result of his critical reading of this manuscript. Marc Heyns and Dr. Michiel Hillen were the source of much practical advice concerning experiments and also of many of the computer programs used in this work. Marc, especially, gave generously of his time to discuss results and ideas. I would like to thank both of them as well as my other colleagues from the 'oxides' group at Leuven, in particular Josiane Vandenbroek and Ivan Darakchiev, for their friendship and collaboration. Thanks, also, to Paul Heremans and Guido Groeseneken for help with the charge pumping measurements.

I am indebted to Mario Reybrouck for sample preparation, always done with great care and skill and similarly to Albert Debie who built several of the measurement systems and maintained them all in excellent working condition. Tom Buytaert and Marleen Tempels have also assisted in numerous ways over the past year. Thanks also to Georges Dubuisson for drawing a number of the figures, to Dr. Christopher Morley for proof reading the final manuscipt and to Mrs.M.Morley for last minute typing of the figure captions. Finally, I am grateful to my flat-mate Huang Qiuting for putting up with me during the traumatic writing-up stage and for being such a calming influence.

|  |   |  | • |  |

|--|---|--|---|--|

|  |   |  |   |  |

|  |   |  |   |  |

|  | • |  |   |  |

|  |   |  |   |  |

|  |   |  |   |  |

|  |   |  |   |  |

|  |   |  |   |  |

|  |   |  |   |  |

|  |   |  |   |  |

|  |   |  |   |  |

|  |   |  |   |  |

|  |   |  |   |  |

|  |   |  | • |  |

#### **ABSTRACT**

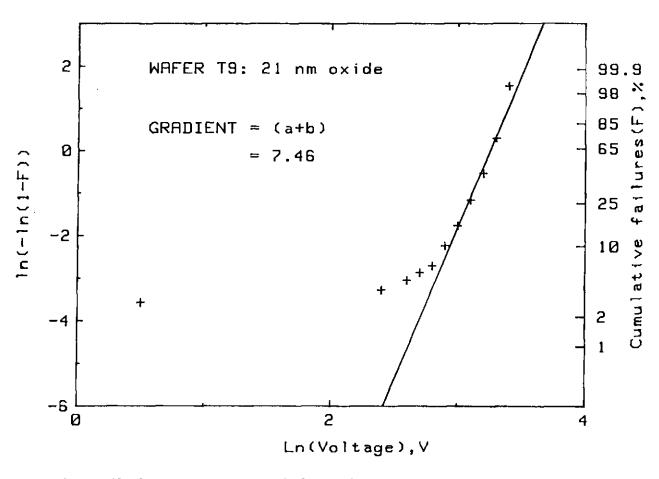

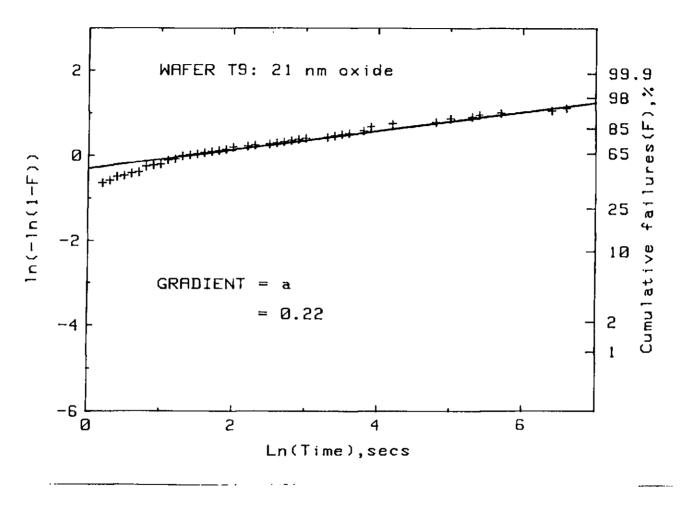

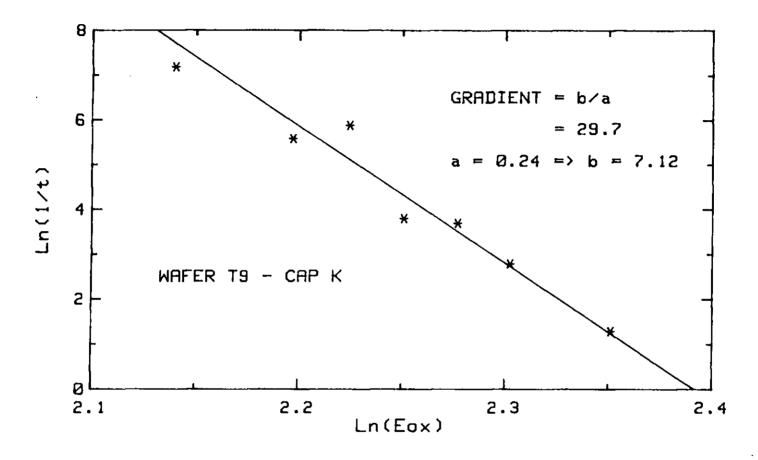

Several aspects of breakdown and charge trapping in silicon dioxide (SiO<sub>2</sub>) have been studied. Firstly, the locations of charge trapped immediately prior to breakdown and of defects created under the high field stress were established using the photo I-V and avalanche injection techniques. Both positive and negative charge was found and in all cases charge build-up under high field conditions was at the interfaces, not in the bulk of the SiO2. Electron trap creation occurred predominantly near to the non-injecting interface.  $Q_{\mathrm{bd}}$ , the total charge which can be injected prior to breakdown. was examined under different current injection conditions. It was found to be strongly dependent on the duty cycle, the temperature and the gate electrode and to vary as  $1/E_{\rm OX}$ , where  $E_{\rm OX}$  is the average field across the oxide. The Weibull distribution was found to describe well the statistics of breakdown in both wearout and dielectric strength measurements. It was shown that the Weibuli parameters a and b have the same values whichever of these methods is used to measure them. The breakdown mechanism is probably the same in both wearout and dielectric strength measurements, therefore.

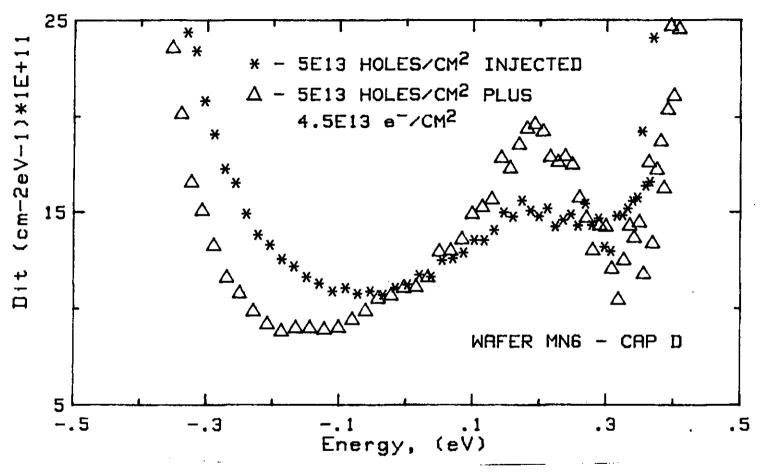

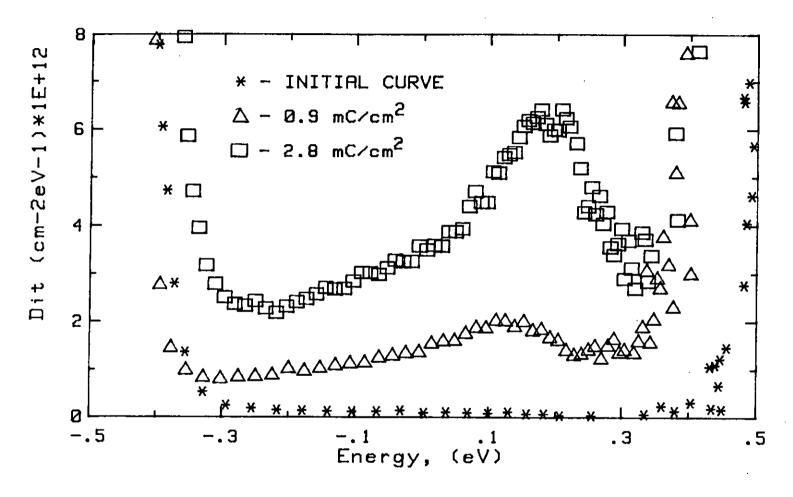

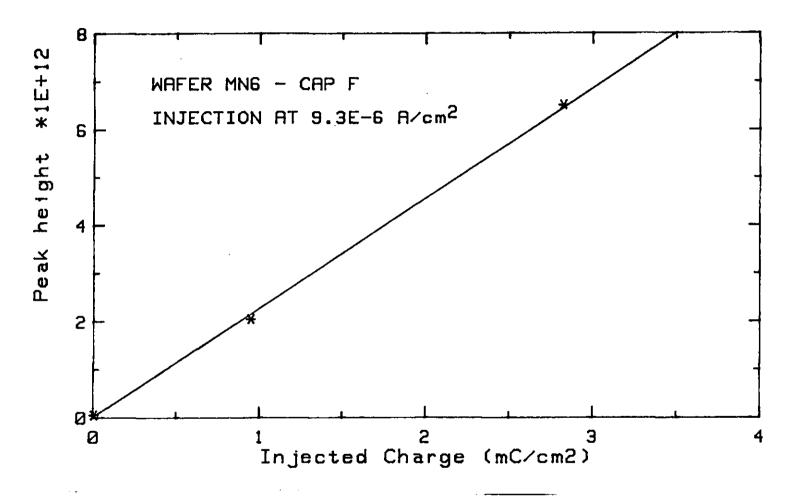

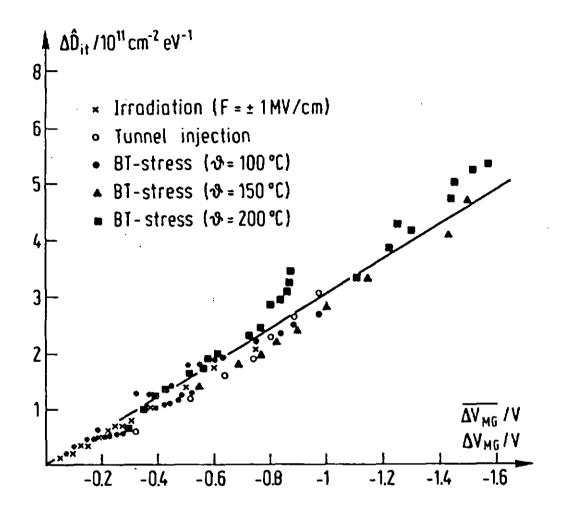

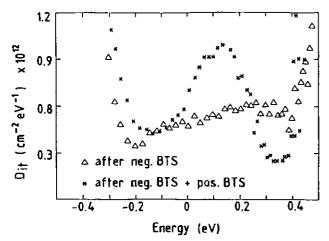

Oxide degradation was also examined under the less severe conditions of bias-temperature stress (BTS). It was shown, using avalanche hole injection before and after negative BTS, that the positive charge generated during negative BTS is due to trapping of holes in intrinsic hole traps. This is accompanied by interface state generation across the whole band gap. The density of these states is linearly proportional to the number of holes trapped. On subsequent application of a positive BTS, the holes were all detrapped or neutralised. At this time a peak also appeared in the interface state density at ~0.2 eV above midgap. This may be due to a redistribution of previously generated states rather than to the creation of new states. The charge pumping technique was used to show that the peak is in fact due to interface states and not to lateral non-uniformities in the surface potential.

## CONTENTS

| CHAPTER 1: INTRODUCTION                                        | 1  |

|----------------------------------------------------------------|----|

| 1.1 The MOS capacitor                                          | 4  |

| 1.2 Breakdown of silicon dioxide layers                        | 6  |

| 1.3 Charged defects in silicon dioxide layers                  | 10 |

| 1.4 The negative bias instability                              | 13 |

| CHAPTER II: EXPERIMENTAL TECHNIQUES AND ANALYSIS               | 17 |

| 2.1 Sample preparation                                         | 17 |

| 2.2 Breakdown measurements                                     | 23 |

| 2.2.1 Dielectric strength                                      | 23 |

| 2.2.2 Time dependent dielectric breakdown                      | 25 |

| 2.2.3 Multi-probe breakdown detection system                   | 25 |

| 2.3 Charge injection and sensing techniques                    | 27 |

| 2.3.1 Fowler~Nordheim tunneling                                | 28 |

| 2.3.2 Avalanche electron injection                             | 29 |

| 2.3.3 Avalanche hole injection                                 | 30 |

| 2.3.4 Internal photoemission                                   | 31 |

| 2.3.5 Measurement systems                                      | 33 |

| 2.3.5.1 Avalanche injection system                             | 34 |

| 2.3.5.2 Photo I-V system                                       | 36 |

| 2.4 C-V and charge pumping measurements                        | 37 |

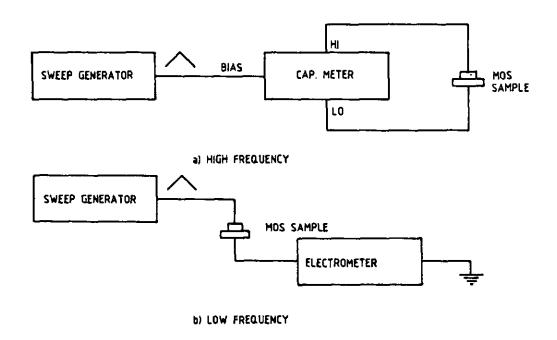

| 2.4.1 High frequency (HF) C-V measurements                     | 39 |

| 2.4.2 Low frequency and quasi-static (QS) measurements         | 41 |

| 2.4.3 $D_{	ext{it}}$ distribution from QS and ideal C-V curves | 42 |

| 2.4.4 D <sub>it</sub> distribition from QS and HF C-V curves   | 42 |

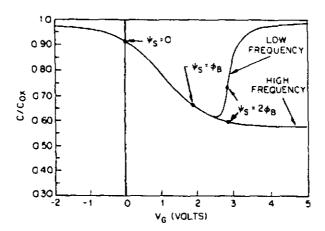

| 2.4.5 BTS measurement system                                   | 43 |

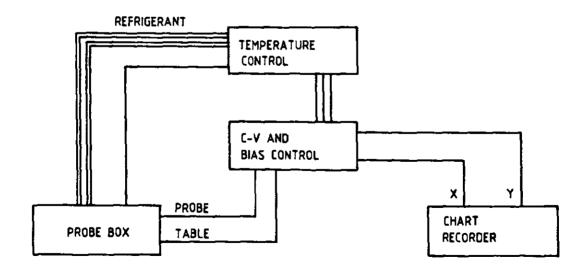

| 2.4.6 Charge pumping measurements                              | 44 |

| CHAPTER III: BREAKDOWN OF SILICON DIOXIDE        | 48   |

|--------------------------------------------------|------|

| 3A: LITERATURE SURVEY                            | 48   |

| 3A.1 Defect-related breakdown                    | 49   |

| 3A.1.1 Nature of defects                         | 49   |

| 3A.1.2 Processing and materials dependence       | 50   |

| 3A.1.3 Sodium-related breakdown                  | 52   |

| 3A.1.4 Area dependence                           | 53   |

| 3A.1.5 Field, time and temperature dependence    | 54   |

| 3A.2 Intrinsic breakdown                         | 56   |

| 3A.2.1 Processing and materials dependence       | 56   |

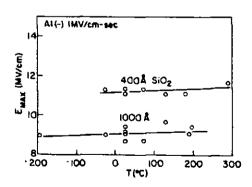

| 3A.2.2 Dependence on measurement parameters      | 58   |

| 3A.2.3 Physical models                           | 59   |

| 3A.2.3.1 Impact ionization model                 | 60   |

| 3A.2.3.2 Anode hole injection model              | 62   |

| 3A.2.3.3 Electron trapping model                 | . 62 |

| 3A.2.3.4 Resonant tunneling model                | 65   |

| 3A.2.3.5 Gas discharge model                     | . 67 |

| 3A.3 Breakdown statistics                        | . 68 |

| 3A.3.1 Breakdown mechanism                       | . 69 |

| 3A.3.2 Extreme value statistics                  | . 70 |

| 3A.3.3 Log normal statistics                     | 73   |

| 3B: RESULTS AND DISCUSSION                       | . 74 |

| 3B.1 Charge trapping preceding breakdown         | . 74 |

| 3B.1.1 Ramp I~V measurements                     | . 74 |

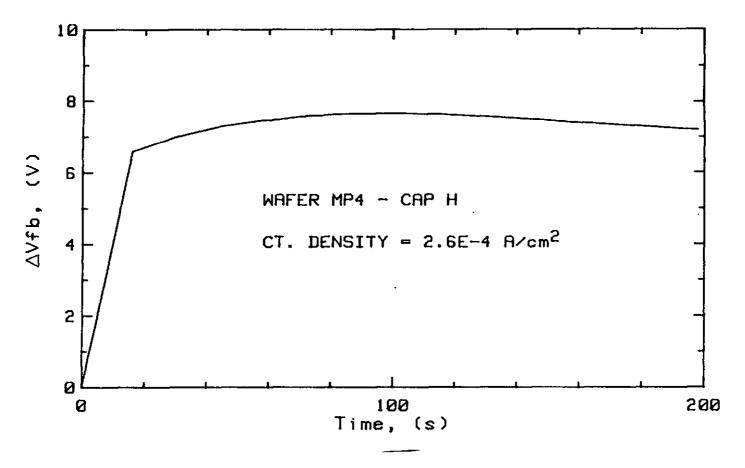

| 3B.1.2 AV <sub>fb</sub> during high field stress |      |

|                                                  |      |

|       |               | 3B.1.3                              | Photo I-V measurements                                                                                                                                                                                                 | 11                                                           |

|-------|---------------|-------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|

|       |               | 3B.1.4                              | Model of charge build-up                                                                                                                                                                                               | 79                                                           |

|       | ٠             | 3B.1.5                              | Discussion of breakdown models                                                                                                                                                                                         | 80                                                           |

|       | 3B.2          | Charge                              | to breakdown under constant current stress                                                                                                                                                                             | <b>8</b> 2                                                   |

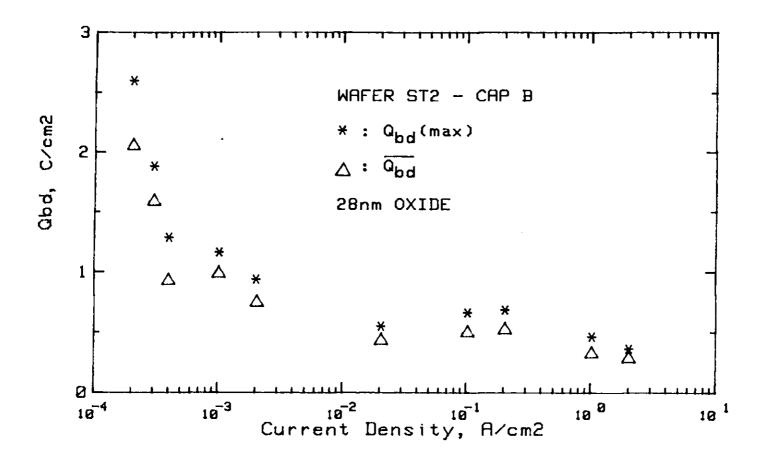

|       |               | 3B.2.1                              | Variation of Q <sub>bd</sub> with current density                                                                                                                                                                      | 82                                                           |

|       |               | 3B.2.2                              | Dependence of $Q_{\mbox{\scriptsize bd}}$ on duty cycle                                                                                                                                                                | 85                                                           |

|       |               | 38.2.3                              | Electrode dependence of $Q_{\mbox{\scriptsize bd}}$                                                                                                                                                                    | 87                                                           |

|       |               | 3B.2.4                              | Temperature dependence of $Q_{\mbox{\scriptsize bd}}$                                                                                                                                                                  | 88                                                           |

|       |               | 3B.2.5                              | Q <sub>bd</sub> and breakdown models                                                                                                                                                                                   | 88                                                           |

|       | 3B <b>.</b> 3 | Relatio                             | onship of TDDB to dielectric strength                                                                                                                                                                                  | 89                                                           |

|       |               | 3B.3.1                              | Applicability of Weibull distribution                                                                                                                                                                                  | 90                                                           |

|       |               | 3B.3.2                              | Analysis of wearout data                                                                                                                                                                                               | 91                                                           |

|       |               | 38.3.3                              | Analysis of dielectric strength data                                                                                                                                                                                   | 91                                                           |

|       |               | 25 2 h                              | Otrailliana and black Halbull annumbers                                                                                                                                                                                | 00                                                           |

|       |               | 38.3.4                              | Significance of the Weibull parameters                                                                                                                                                                                 | 92                                                           |

| CHAP' | TER I         |                                     | NEGATIVE BIAS INSTABILITY                                                                                                                                                                                              |                                                              |

|       |               | V: THE                              |                                                                                                                                                                                                                        | 20                                                           |

|       | LITE          | V: THE                              | NEGATIVE BIAS INSTABILITY 1                                                                                                                                                                                            | 20                                                           |

|       | LITE          | V: THE<br>RATURE:<br>Bias-t         | NEGATIVE BIAS INSTABILITY                                                                                                                                                                                              | 20<br>  20<br>  21                                           |

|       | LITE          | V: THE<br>RATURE:<br>Bias-t         | NEGATIVE BIAS INSTABILITY                                                                                                                                                                                              | 20<br>  2 <b>0</b><br>  2 <b>1</b>                           |

|       | LITE          | V: THE<br>RATURE:<br>Bias-t         | NEGATIVE BIAS INSTABILITY  SURVEY  emperature stressing of MOS capacitors  Measurement of the voltage shift                                                                                                            | 20<br>  2 <b>0</b><br>  2 <b>1</b><br>  21                   |

|       | LITE          | V: THE<br>RATURE:<br>Bias-t         | NEGATIVE BIAS INSTABILITY                                                                                                                                                                                              | 20<br>  20<br>  21<br>  21<br>  21                           |

|       | LITE          | V: THE<br>RATURE:<br>Bias-t         | NEGATIVE BIAS INSTABILITY  SURVEY  emperature stressing of MOS capacitors  Measurement of the voltage shift  Kinetics of $\Delta V_{fb}$ and $\Delta V_{mg}$                                                           | 20<br> 20<br> 21<br> 21<br> 21<br> 21                        |

|       | LITE          | V: THE RATURE: Bias-t 4A.1.1 4A.1.2 | NEGATIVE BIAS INSTABILITY  SURVEY  emperature stressing of MOS capacitors  Measurement of the voltage shift  Kinetics of $\Delta V_{fb}$ and $\Delta V_{mg}$ 4A.1.2.1 Time dependence  4A.1.2.2 Temperature dependence | 20<br> 2 <b>0</b><br> 2 <b>1</b><br> 21<br> 21<br> 21<br> 22 |

|     | 4A.2         | Processing dependence of the neg. bias instability 125                      |  |

|-----|--------------|-----------------------------------------------------------------------------|--|

|     |              | 4A.2.1 Oxidation conditions                                                 |  |

|     |              | 4A.2.2 Effect of anneals 127                                                |  |

|     |              | 4A.2.3 Gate electrode dependence                                            |  |

|     | <b>4A.</b> 3 | Models for the negative bias instability 129                                |  |

|     |              | 4A.3.1 Hole trapping model 129                                              |  |

|     |              | 4A.3.2 Electron emission model                                              |  |

|     |              | 4A.3.3 Excess silicon model                                                 |  |

|     |              | 4A.3.4 Oxygen vacancy model                                                 |  |

|     |              | 4A.3.5 Valence alteration pair model 134                                    |  |

|     |              | 4A.3.6 Others models                                                        |  |

| 4B: | RESU         | TS AND DISCUSSION                                                           |  |

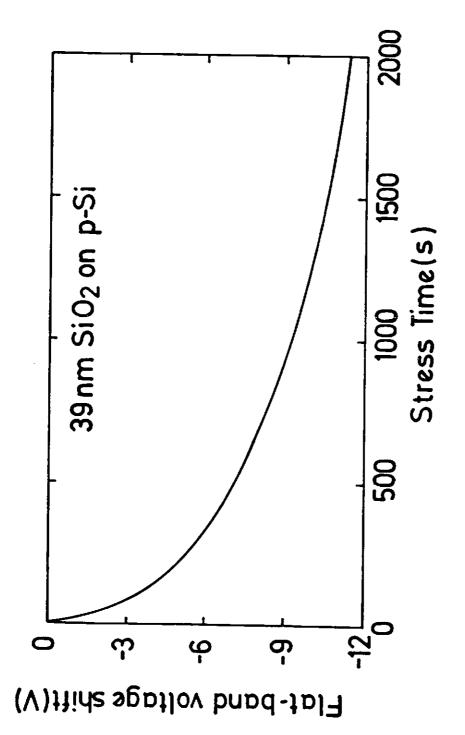

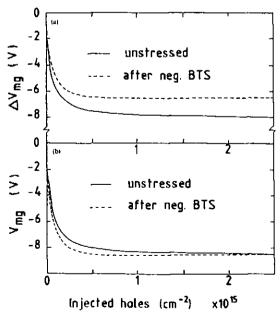

|     | 4B.1         | Kinetics of positive charge generation                                      |  |

|     |              | 4B.1.1 Hysteresis in C-V curves and loss of $Q_{\mathrm{ot}}(+)$ 137        |  |

|     |              | 4B.1.2 Use of $\Delta V_{mg}$ to measure oxide charge 138                   |  |

|     |              | 4B.1.3 Location of Q <sub>ot</sub> (+)                                      |  |

|     |              | 4B.1.4 Time dependence of $\Delta V_{mg}$                                   |  |

|     |              | 4B.1.5 Temperature dependence of $\Delta V_{mg}$                            |  |

|     |              | 4B.1.6 Field dependence of $\Delta V_{mg}$                                  |  |

|     |              | 4B.1.7 Electrode dependence of $\Delta V_{mg}$                              |  |

|     | 4B.2         | Positive charge generation and hole trapping 143                            |  |

|     |              | 4B.2.1 Correlation between $\Delta V_{mg}(BTS)$ and $\Delta V_{mg}(AI)$ 143 |  |

|     |              | 4B.2.2 $\Delta V_{mg}$ (BTS) and filling of intrinsic hole traps 143        |  |

|     |              | 4B.2.3 Removal of positive charge by positive BTS 144                       |  |

|     |              | 4B.2.4 Capture cross sections of hole traps 144                             |  |

|     |              | 4B.2.5 Current flow during negative BTS 145                                 |  |

|     |              | 4B.2.6 Effect of gate electrode on hole trapping 146                        |  |

|     |              | 4B.2.7 Discussion of models for hole trapping 148                           |  |

| 4B.3 ]     | interface state generation accompanying hole trapping               |                 |

|------------|---------------------------------------------------------------------|-----------------|

|            | and detrapping or neutralisation of trapped holes                   | 151             |

|            |                                                                     |                 |

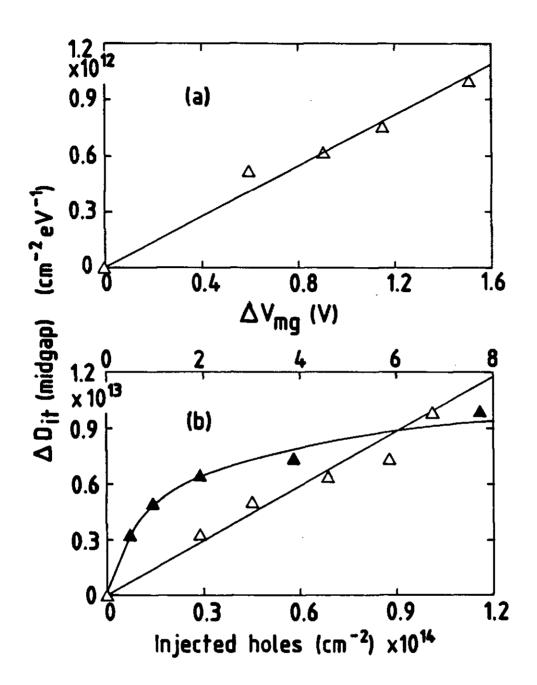

| 1          | B.3.1 ΔD <sub>it</sub> (mg) during negative BTS                     | 151             |

| 1          | $4B.3.2 \Delta D_{it}(mg)$ during avalanche hole injection          | 152             |

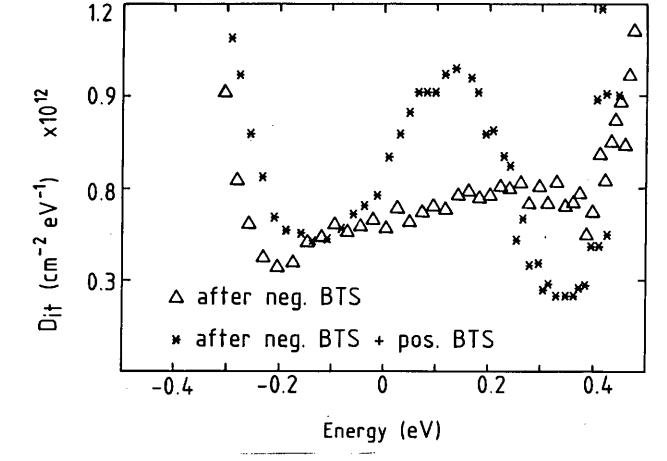

| 1          | $^{ m IB.3.3~D}_{ m it}$ distribution after negative + positive BTS | 153             |

| 1          | 4B.3.4 D <sub>it</sub> distribution generated by F-N tunneling or   |                 |

|            | irradiation                                                         | 15 <sup>L</sup> |

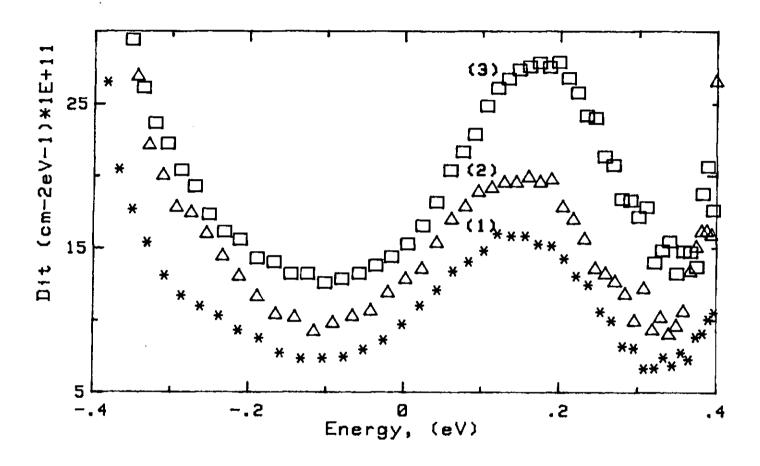

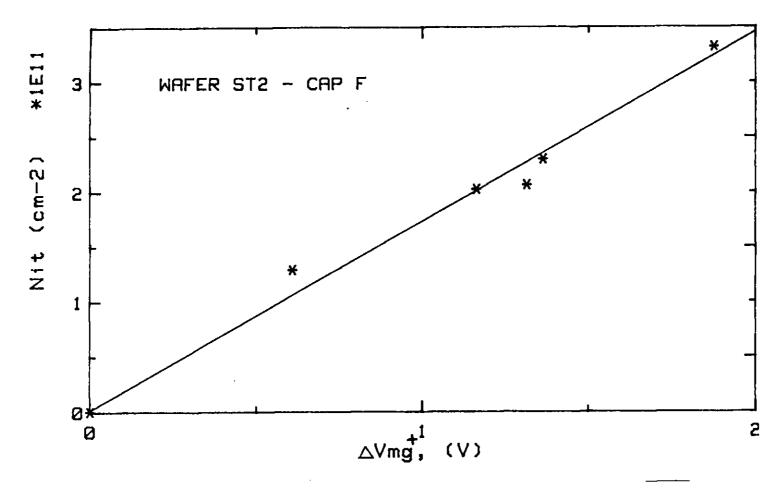

| 1          | ${\tt B.3.5~D}_{	ext{it}}$ distributions measured by charge pumping | 155             |

| 1          | B.3.6 Nature of interface states generated by hole                  |                 |

|            | trapping                                                            | 156             |

| CHAPTER V: | CONCLUSIONS AND SUGCESTIONS FOR FURTHER WORK                        | <b>1</b> 91     |

| REFEREI    | 1CES                                                                |                 |

**PUBLICATIONS**

## CHAPTER ONE: INTRODUCTION

Amorphous silicon dioxide  $(SiO_2)$  is widely used as an insulator in integrated circuits because of its high dielectric strength and its relative ease of formation within planar silicon processing technology. It also finds applications as a surface passivation layer and as a diffusion barrier during the doping of silicon. Thermally grown  $SiO_2$  has the best characteristics for electrical isolation purposes and this is generally used in active areas such as for the gate dielectric of an EAROM (Electrically Alterable Read Only Memory) or of a MOSFET (Metal Oxide Semiconductor Field Effect Transistor) where relatively high electric fields are likely to be encountered.

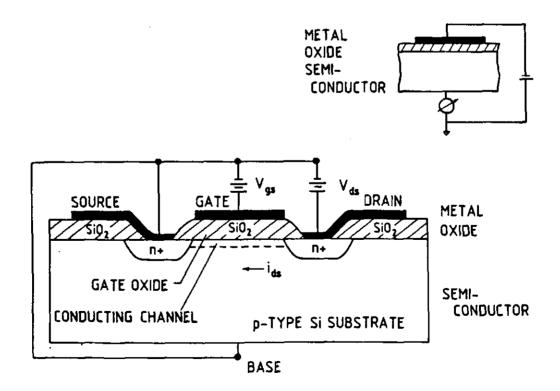

Figure 1.1 shows a simplified diagram of an n-channel (enhancement mode) MOSFET illustrating the role of SiO<sub>2</sub> in the operation of the device. Inset is the simpler MOS capacitor stucture.

Figure 1.1 N-channel enhancement mode MOSFET and MOS capacitor.

#### INTRODUCTION

The electric field at the  $Si-SiO_2$  interface is controlled by the bias applied to the gate and the properties of the channel, a layer in the silicon adjacent to the interface, are thereby determined. At zero gate bias this region is p-type and does not conduct. No current will flow between source and drain although there is a voltage drop between them. However, when the voltage applied to the gate exceeds a certain threshold level,  $V_T$ , the channel region becomes inverted to n-type. Thus, there is now a conducting layer allowing current to flow between source and drain.

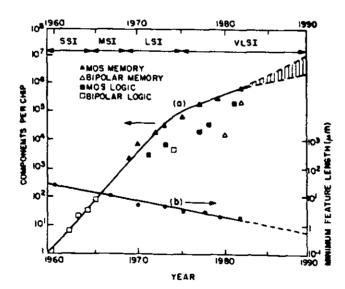

The number of transistors in an MOS integrated circuit (IC) has increased exponentially since 1960 (Fig.1.2, curve (a)). Although the rate of growth has slowed down over recent years, extrapolation from past trends still suggests that a one megabit memory chip (i.e. one million devices per IC) will be in production before 1990 (1). This is certainly a realistic estimate since such circuits have already been made at research level (2,3). The most important factor in achieving increased complexity is reduction of the minimum device dimensions (Fig.1.2, curve (b)) (4).

Figure 1.2 (a) Growth in number of components per chip (1) and (b) Minimum device dimensions achieved since 1960 (4).

Scaling to smaller dimensions and the resulting higher level of integration which can be obtained reduces cost, gives higher operating speeds and lowers power consumption. For very large scale integration (VLSI), with  $>\!10^5$  components per chip, high quality oxide layers of between 1D and 50 nm are required for the gate insulator. It is the properties of these thin thermally grown  $\rm SiO_2$  layers that will be considered in the present work.

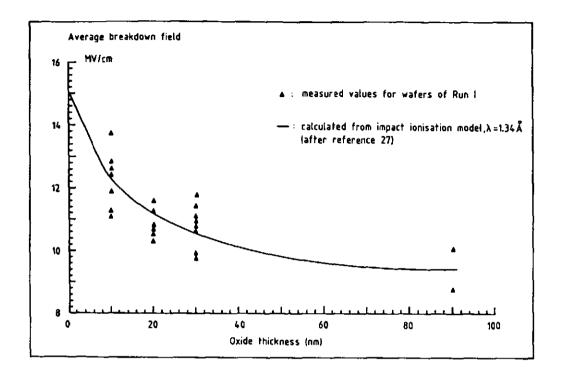

Several consequences for the SiO<sub>2</sub> layer arise from device To begin with, some properties of the oxide may change as its thickness is reduced. For example, an advantage of thin oxides is that the maximum breakdown field increases with decreasing thickness (5,6). On the other hand defect densities (7,8) and interface trap densities (9) have been reported to increase thus reducing device reliability. The dielectric constant also seems to be different for very thin oxide layers (9,10). Furthermore, the voltage used for operation is often not scaled linearly with the oxide thickness so that the insulator may have to withstand higher applied fields. If this increase in field is severe it may increase the probability of electrical breakdown occurring during operation despite the reduced field sensitivity of thin oxides. There is also a greater chance of energetic electrons (or holes) being injected into the oxide from the channel and becoming trapped at defect sites or generating new defects in the oxide. More rapid degradation of the device characteristics may then result. Aspects of all the latter problems, breakdown, charge trapping and trap generation have been addressed in the course of this work.

Most measurements have been carried out on MOS capacitors rather than transistors. This simpler structure comprises the active region of the transistor (inset Fig.1.1) and requires fewer processing steps which is advantageous to the study of the intrinsic properties of the oxide layer.

## 1.1 The MOS capacitor.

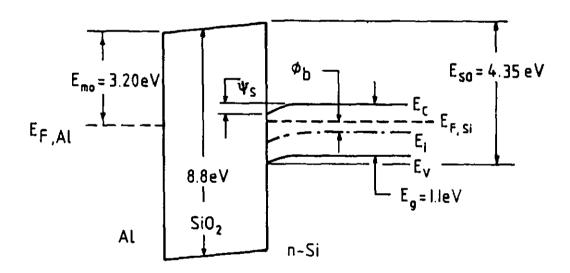

The energy band diagram of an MOS capacitor with an aluminium gate electrode is shown in Fig.1.3. The physics of this device is discussed extensively in reference (11). Conduction is limited by the height of the energy barrier for excitation of electrons into the oxide conduction band, making the  $SiO_2$  an excellent insulator. Since the barrier to hole injection is at least 1 eV higher than for electrons there will be negligible current due to hole conduction, especially as the hole mobility is also very low in  $SiO_2$  (2 x  $10^{-5}$  cm<sup>2</sup>/Vs).

Figure 1.3 Energy band diagram of an MOS capacitor with an aluminium gate electrode (after (11).)

When the gate is connected to the substrate an internal electric field is maintained as a result of the difference in the work functions of aluminium and silicon. This work function difference,  $\phi_{ms}$ , is given by:

$$q\phi_{ms} = E_{mo} - E_{so} + E_{g}/2 + q\phi_{b}$$

where  $E_{mo}$  and  $E_{so}$  are the energy barriers at the metal and silicon interfaces respectively.  $E_g$  is the bandgap and  $\phi_b$ , the Fermi level in the silicon bulk. The sum of the band bending at the surface and the Fermi level,  $\psi_s$  +  $\phi_b$ , is the electrostatic potential at the surface or the surface potential,  $\phi_s$ . If a gate voltage is applied to the device such that the band bending is zero, the so-called flatband condition is attained and the applied voltage is known as the flatband voltage ( $V_{fh}$ ).

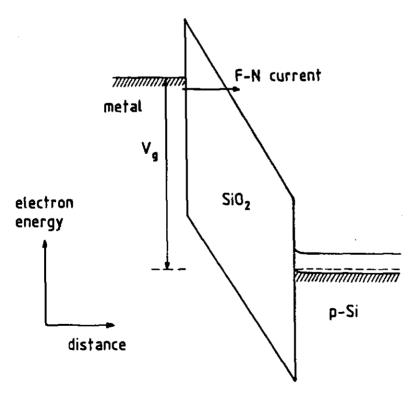

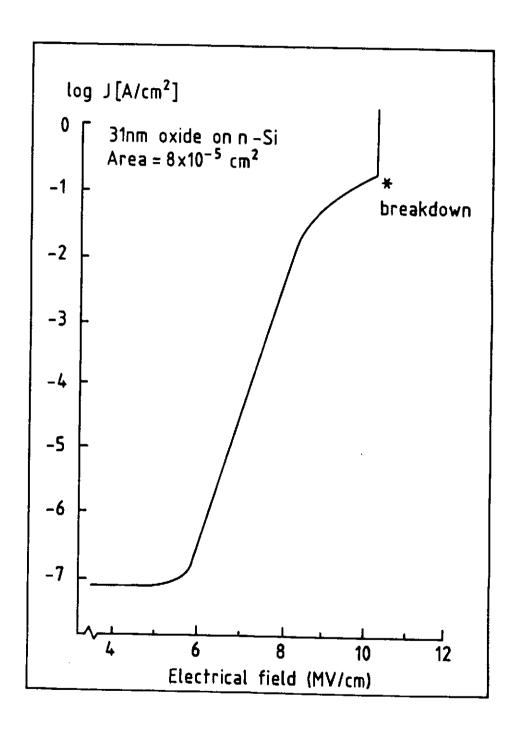

Although the energy barriers to conduction are high, once electrons enter the oxide conduction band they are quite mobile (-20cm²/Vs at room temperature) and can flow under the influence of an electric field. At fields in excess of -6MV/cm significant electron injection may occur due to Fowler-Nordheim (F-N) tunneling (12). Electrons from the metal or silicon conduction bands can tunnel through the triangular barrier at the interface which becomes narrower as the field is increased (Fig.1.4).

Figure 1.4 F-N tunneling into the SiO2 conduction band.

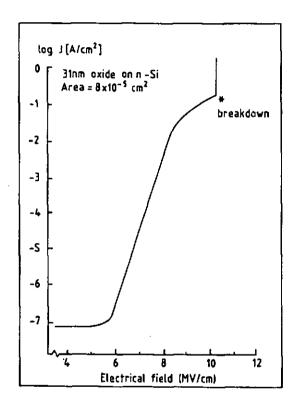

Quite high currents may flow (up to  $-60 \text{A/cm}^2$ ) before the oxide breaks down. As the field is further increased however destructive breakdown eventually occurs. This is characterised by a sudden increase in current and loss of the insulating properties of the  $\text{SiO}_2$  so that even when the applied field is lowered high leakage currents flow. A typical I-V curve measured on capacitor J on wafer JN1 and illustrating F-N tunneling and breakdown is displayed in Fig.1.5.

Figure 1.5 I-V curve for an MOS capacitor showing the displacement current, F-N tunneling current and breakdown.

## 1.2 Breakdown of SiO2 layers.

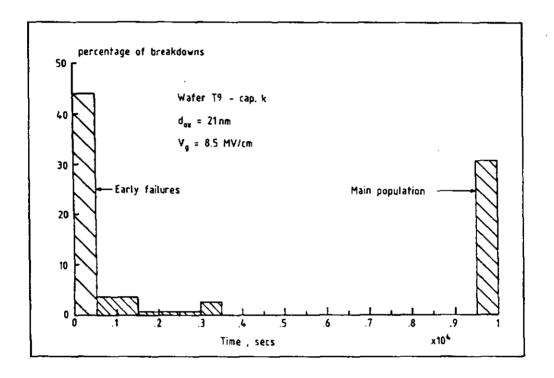

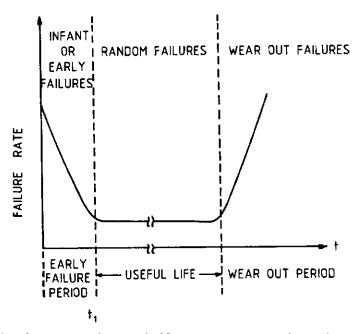

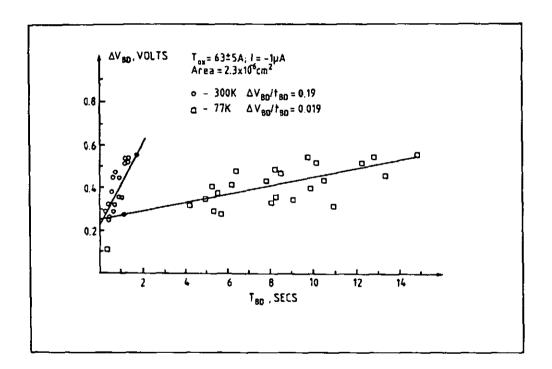

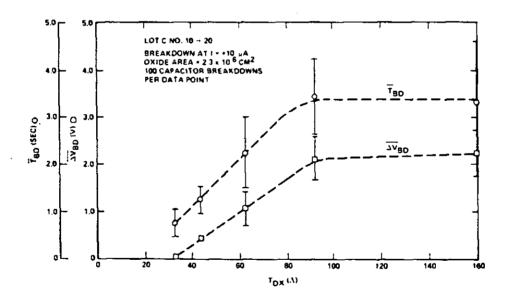

Breakdown has largely been studied by means of two types of experiment. In a time dependent dielectric breakdown (TDDB) or wearout measurement, a constant voltage (13) or constant current (8) stress is applied and the time to breakdown measured. Typically a bimodal distribution is found (Fig.1.6). The early device failures are due to electrically active defects in the oxide which allow a

conducting pathway to form more readily on application of a bias. Constant voltage wearout measurements are frequently used to assess the reliability of  $SiO_2$  layers under device working conditions. Extrapolation may be made from test conditions using elevated fields and temperatures to the normal operating situation (14).

Figure 1.6 Example of a bimodal distribution typically observed for TDDB of MOS capacitors.

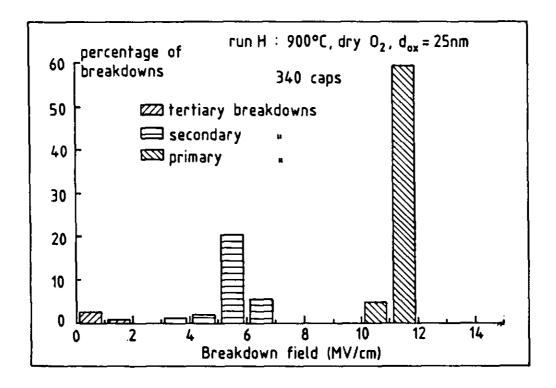

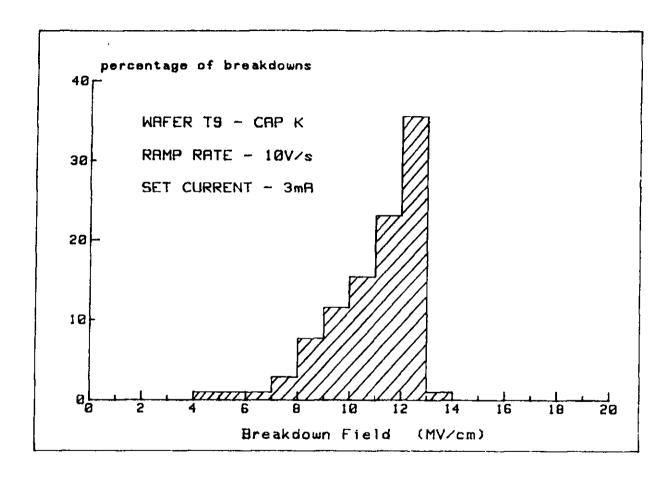

Another type of experiment commonly used to examine oxide integrity is the dielectric strength measurement. Here a fast voltage ramp is applied to each of a number of capacitors and the field at which breakdown occurs is measured. A statistically valid sample size, usually ≥100 devices, is taken and the results are presented in the form of a histogram. (This experiment is sometimes referred to as a 'breakdown' measurement. We shall however reserve the term breakdown for the actual destruction of the insulator which occurs in both wearout and dielectric strength measurements.) Breakdown is usually defined in a dielectric strength measurement as the exceeding

#### INTRODUCTION

of a certain preset current. In order for this to be a valid definition, the current must be chosen carefully to ensure that irreversible failure has occurred i.e. that it is breakdown and not merely tunneling injection which is being observed. Three peaks are frequently observed in the resulting failure distribution (15,16). A typical histogram is shown in Fig. 1.7 for cap. J on wafer H1.

Figure 1.7 Breakdown histogram showing the three peaks commonly observed in a dielectric strength measurement.

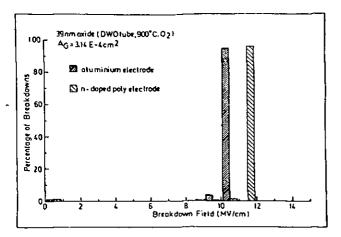

The low field breakdowns (tertiary peak) have been attributed to gross structural defects such as pinholes. Medium field breakdowns (secondary peak) are most probably caused by smaller scale structural defects or impurities. The high field (primary) peak has frequently been assumed to represent intrinsic breakdown of the  $\mathrm{SiO}_2$ . However, the slight effect of processing conditions on the position and width of this peak (17) and the increase in the maximum breakdown field ( $\mathrm{E}_{\mathrm{bd}}$ (max)) achieved over recent years (18), suggest that this point may not yet have been reached. Very small scale defects, perhaps

broken bonds or trapped charges, probably also play a role in causing high field breakdown and in determining the lifetime of a device under wearout conditions. Certainly TDDB has been shown not to be determined by the oxide alone but to be a property of the  $SiO_2$ -electrode system (19). Higher breakdown fields have also been achieved, at least at negative polarity, using the corona discharge technique rather than metal electrodes (20). The effect of processing and materials on breakdown and also its dependence on measurement parameters are discussed further in sections 3A.1 and 3A.2.

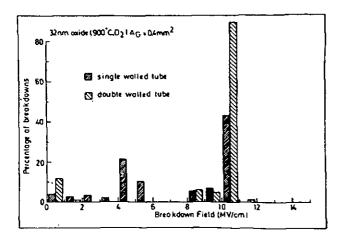

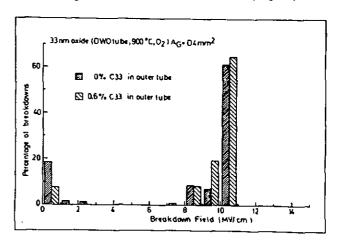

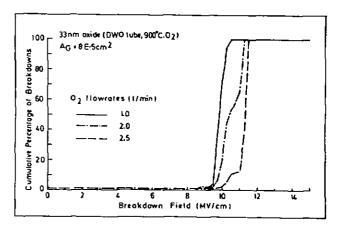

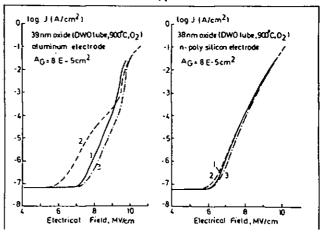

As device dimensions are scaled down and the SiO<sub>2</sub> thickness is reduced, the defect density (defined empirically in terms of those defects and impurities resulting in low and medium field breakdowns) tends to go up, causing yield problems. In part this problem can be solved by using extremely clean processing conditions. For example, use of a double-walled oxidation tube (DWO) removes most medium field breakdowns (21). This is thought to be because metallic impurities are carried away by the gas flow in the outer tube and thereby prevented from diffusing into the oxidation tube itself (22).

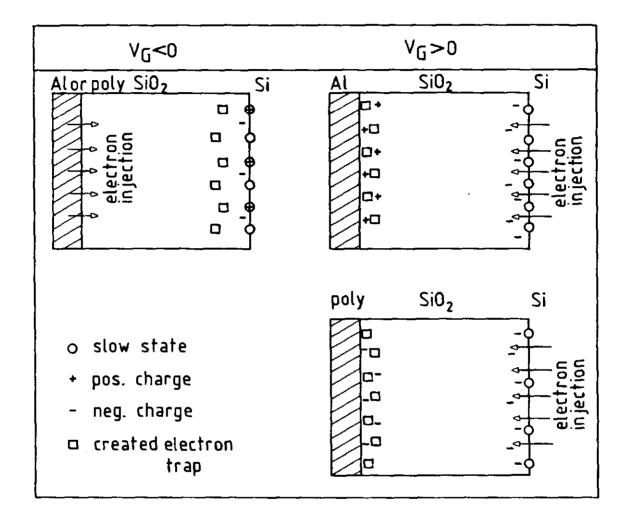

The primary peak moves to higher fields on reduction of the oxide thickness (23,24). The reason for this is not known and neither is the breakdown mechanism in this region well understood. Various models for intrinsic breakdown can be found in the literature. These fall essentially into two categories, those based on the build-up of positive charge, such as the impact ionisation model (25-29) and those based on electron trapping, such as the electron trap generation model of Harari (8,30) and the microplasma breakdown model of Budenstein (31) and Wolters (32,33). In section 3A.2.3 these will be considered in more detail, while in 3B.1 experimental evidence will be presented on the nature of the charge build-up occurring under the high oxide fields prevailing immediately prior to breakdown. Both positive and negative charge was observed. All charge trapping and defect generation occurred at or near to the interfaces. There was no evidence for bulk charge trapping under high field conditions.

Various experimental techniques were used for these measurements including high field constant current stress to simulate the pre-breakdown situation, avalanche electron injection (34) to fill oxide traps and internal photoemission (photo I-V) to examine the charge distribution in the oxide (35). These will be discussed in detail in section 2.3, while classical breakdown measurements, dielectric strength and TDDB are considered in 2.2.

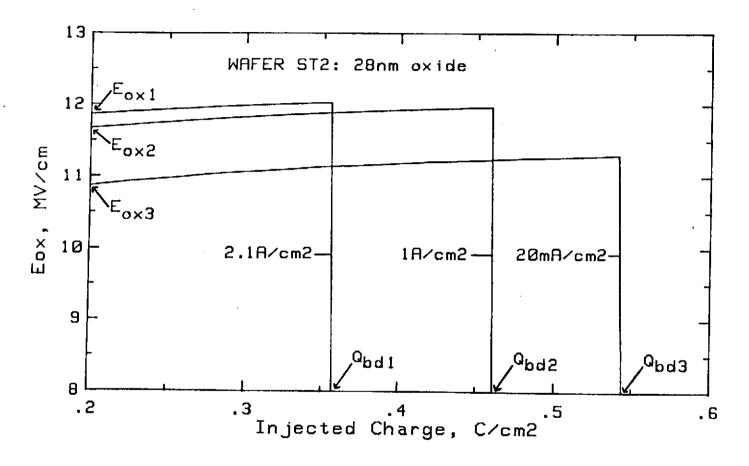

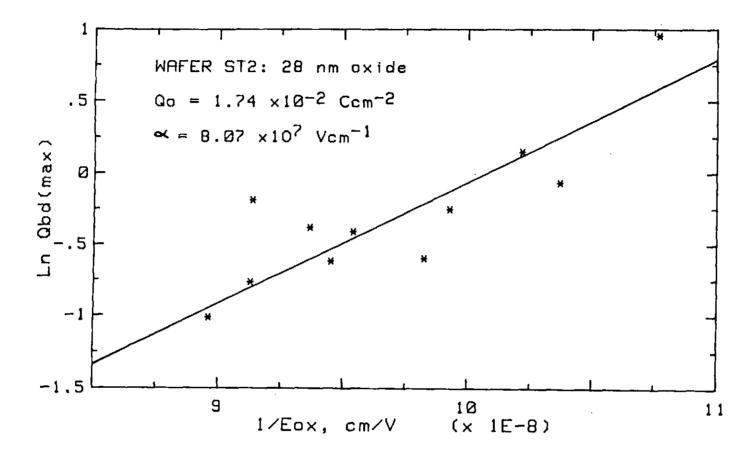

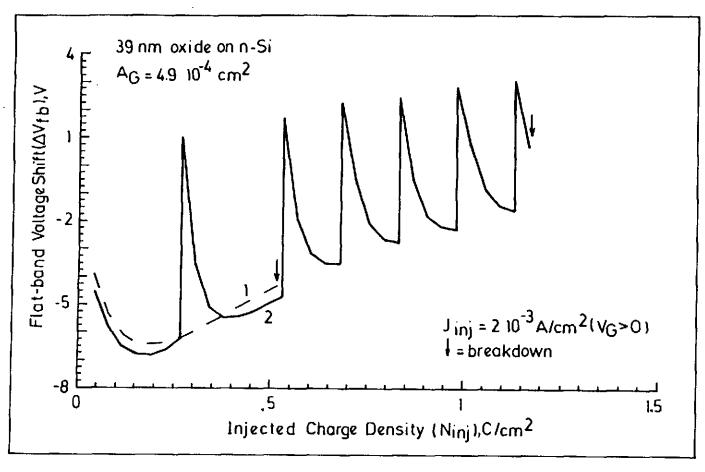

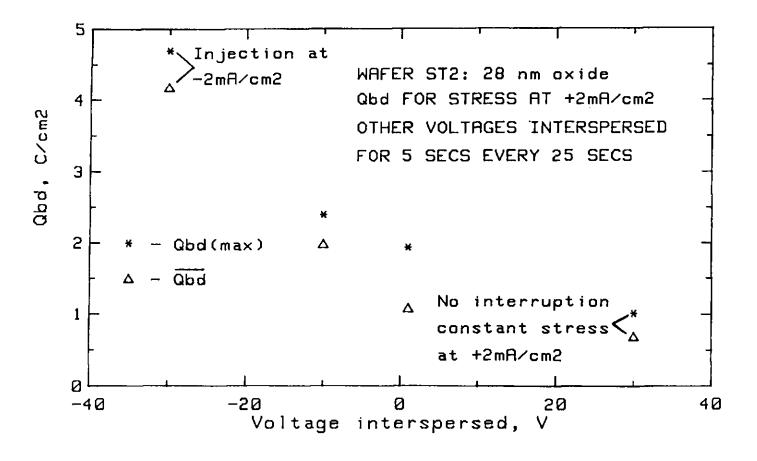

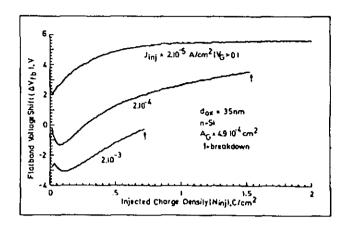

The constant current stress technique offers certain advantages over the more commonly used fast voltage ramp and constant voltage wearout measurements. Firstly, it enables compensation for the varying internal oxide field, which changes as a result of charge trapping, and thereby allows the injecting field to be kept constant. Secondly, the total amount of injected charge prior to breakdown,  $Q_{\mathrm{bd}}$ , can be simply calculated. This is a useful parameter to use in comparing the oxide quality of different samples, providing the injection is carried out at the same current density. It will be shown in 3B.2 that, in a constant current measurement, Qbd Independent of the injection conditions, such as current density and duty cycle, as has been previously suggested (8,36,37). Unlike dielectric strength measurements, wearout also allows examination of the events leading up to breakdown in 'slow motion.' This does presuppose however, that breakdown itself takes place by the same mechanism in a fast voltage ramp measurement as it does under wearout conditions. There is some evidence in the literature that this is indeed the case (14,38,39). To examine this point further, the relationship statistical between dielectric strength time-to-breakdown in a constant voltage wearout measurement was also studied (3B.3).

## 1.3 Charged defects in SiO2 layers.

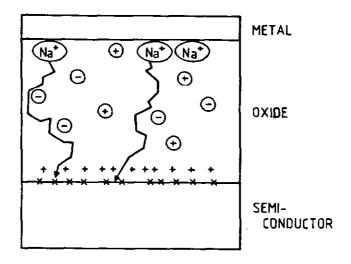

Defects may be present in as-grown oxides or be generated subsequently under various conditions. Apart from any role they may play in enhancing breakdown these defects may have deleterious effects on device operation should they become charged. The Deal notation and classification scheme depicted in Figure 1.8 will be used to define operationally the types of defect which may be found in the MOS system (40).  $Q_{\rm m}$  represents mobile ionic charge, such as alkali ions, which can migrate through the oxide under bias (41), especially if elevated temperatures are used. In particular, sodium is easily introduced from the environment. Contamination of this kind was a severe problem in the early days of silicon technology but it has been largely overcome by the use of very clean processing conditions.

Na Q<sub>m</sub> - MOBILE IONIC CHARGE + Q<sub>f</sub> - OXIDE FIXED CHARGE x Q<sub>if</sub> - INTERFACE TRAP CHARGE ⊕ Q<sub>at</sub> - OXIDE TRAPPED CHARGE

Figure 1.8 Deal notation and classification scheme for charged defects in MOS structures (taken from ref. (42)).

Examples of defects whose charge state may be varied are both fast and slow interface states. The former may be positively or negatively charged or neutral. They are often referred to simply as 'interface states' but they have also been called 'fast states', 'interface traps' or 'surface states'. In Deal's system they are represented by  $Q_{it}$ . They are located physically at the interface and energetically within the silicon bandgap. Consequently, the

charge state of these defects depends on the position of the Fermi level at the interface and hence on the applied voltage. The density of interface traps is usually specified with respect to unit energy within the silicon bandgap, that is in  $/\text{cm}^2\text{eV}$  for which the symbol  $D_{it}$  is used. ( $N_{it}$  is used for  $\int D_{it}.dE$ .)

Interface states are present in as-oxidised samples with a density of the order of  $10^{11}$ - $10^{12}$  /cm²eV (42). Their density is reduced by a post-metallization anneal (PMA) generally performed in forming gas. After this treatment the trap density displays a minimum at midgap with an increase towards both band edges giving a U-shaped distribution. The lowest reported midgap values are around 5 x  $10^8$  to  $10^9$  /cm²eV (43,44). Using electron spin resonance (ESR) Caplan et al. (45) have demonstrated these interface traps to be due to Si $\frac{1}{3}$ Si· species or so-called dangling bonds at the interface. As well as being present in as-processed oxides, interface traps are also produced by various forms of electrical stress e.g. avalanche injection of electrons (46) or holes (47), high field stress (48) or bias-temperature stress (BTS) (48,49) and also by ionising radiation (48,50,51,52). Methods of measuring interface state densities are discussed in section 2.4.

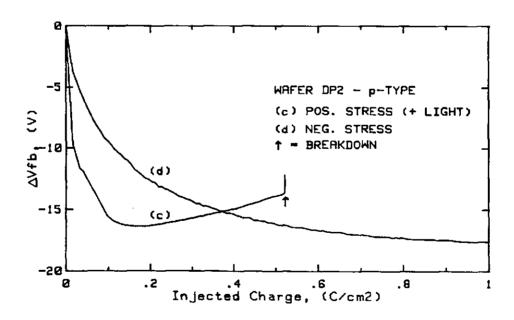

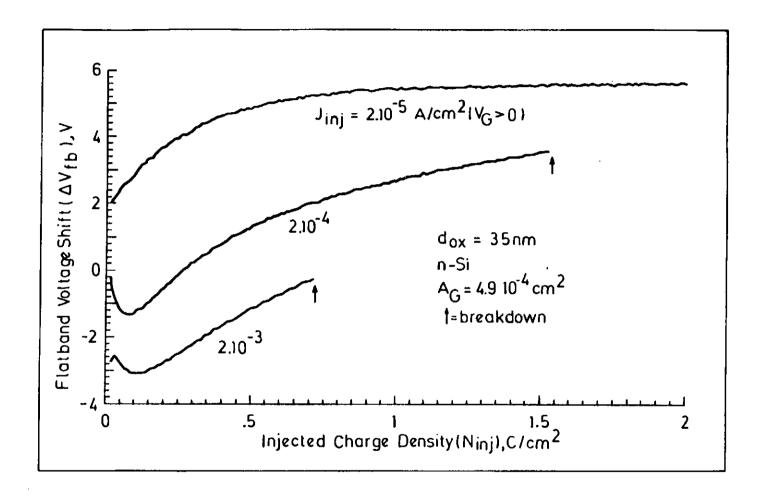

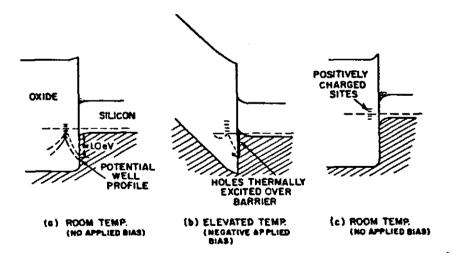

'Slow-states' are also located at or very near to the interface but they respond more slowly to an applied bias. They have been defined somewhat arbitrarily as those not responding to a 1 MHz high frequency C-V sweep at 1 V/s (53). These defects may be either positively charged or neutral and they were first seen in avalanche electron injection experiments where they are responsible for the 'turn-around' effect (54,55). (The flatband voltage shift is initially positive during avalanche electron injection, indicative of electron trapping in the oxide. After injection has continued for a while, however, the shift becomes negative showing the presence of positive oxide charge. This is known as the 'turn-around' effect.) The generation of slow states has now also been observed during injection by F-N tunneling (21) and avalanche injection of holes (56).

Slow-states are converted to a neutral charge state by the application of moderate positive biases or elevated temperatures and positively charged again by negative applied biases.

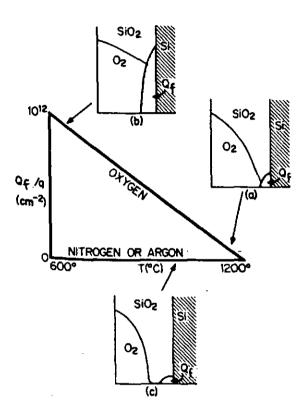

Fixed oxide charge,  $Q_f$ , is another interface related defect, always positive in sign. It appears to be physically further from the interface and/or energetically outside the silicon bandgap, since its occupancy is not a function of applied voltage. Immediately after oxidation,  $Q_f$  is present with a density dependent on the oxidation temperature. Its density is usually of the order of  $\sim 10^{12} \ / \text{cm}^2$  and may by reduced to  $10^{10} - 10^{-11} \ / \text{cm}^2$  by a post-oxidation anneal (POA) in an inert ambient such as nitrogen (N<sub>2</sub>) or argon (Ar) (42).  $D_{it}(\text{init})$ , the initial as-processed interface state density, and  $Q_f$  respond in the same way to oxidation conditions and some but not all annealing treatments (57), implying a connection between them as regards physical origin.

Charge of either sign may be distributed throughout the oxide and is denoted by  $Q_{\rm ot}$  (oxide trapped charge). This oxide charge may be introduced during fabrication, as a result of irradiation and by the same experimental techniques which create interface states: avalanche injection of electrons or holes, high field stress or BTS.

## 1.4 The Negative Bias Instability

Sodium contamination results in an instability in devices under positive bias conditions where drift of Na $^+$  ions to the Si-SiO $_2$  interface results in a positive shift of the threshold voltage, V $_T$ . In devices free of mobile ions, another phenomenon is sometimes observed known as the negative bias instability. Prolonged operation of MOSFETs under negative gate bias, causes both interface states and positive oxide charge (denoted here as  $Q_{ot}(+)$ ) to be generated close to the Si-SiO $_2$  interface resulting in a negative shift of V $_T$  (58). This can threaten the reliability of MOSFETs, especially of p-channel devices (59). As well as causing a V $_T$  shift, drain junction

avalanche breakdown is also affected, being reduced for p-channel and increased for n-channel transistors. Gain or transconductance is reduced by both oxide charge and interface states. A larger change in gate voltage is required to produce a given change in channel conductance when  $D_{it}$  is large. Also the gain depends on the effective mobility of free carriers in the channel and this is reduced by scattering at charged centres. Drain junction leakage current and flicker noise are also increased by interface states.

As device dimensions are reduced, interface effects such as the negative bias instability become relatively more important. Low-cost plastic packaging which is being used increasingly has also been found to enhance the negative bias instability and has thus generated renewed interest in this long-standing problem (60,61). It is thought that the diffusion of water from the packaging or from phosphosilicate glass (PSG) passivation layers may be the cause of this enhanced degradation.

Measuring the shift in the high frequency capacitance-voltage (C-V) curve on an MOS capacitor is a convenient means of studying this instability and application of the bias at elevated temperatures speeds up the ageing process so that experiments can be conducted on a more manageable time-scale. This technique is in fact similar to the wearout measurements discussed in 1.2. In BTS, rather than applying a high bias at room temperature, a more moderate bias is used at elevated temperature. The point of breakdown is not normally reached under the less severe BTS conditions, but both wearout and BTS are essentially ageing techniques.

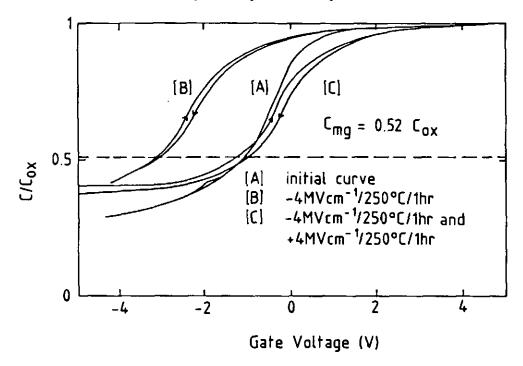

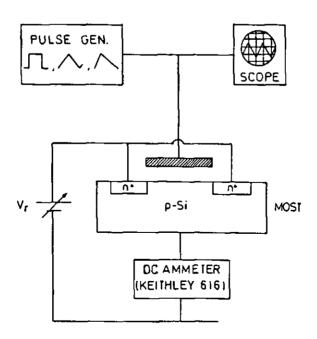

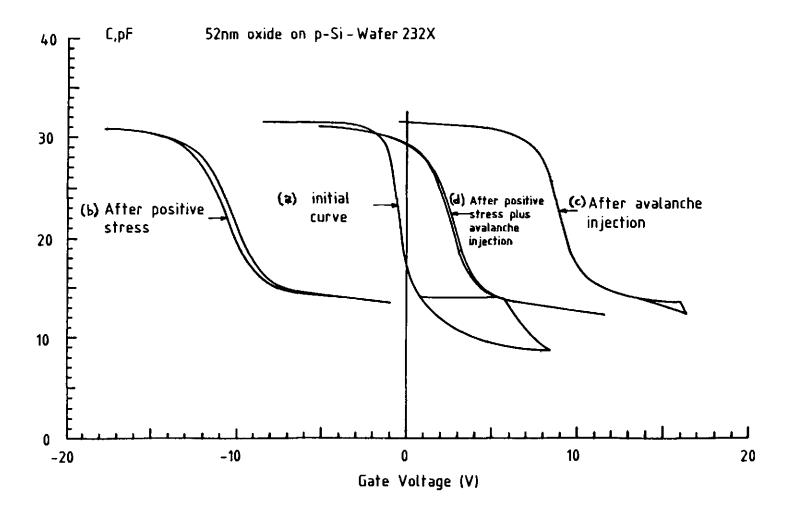

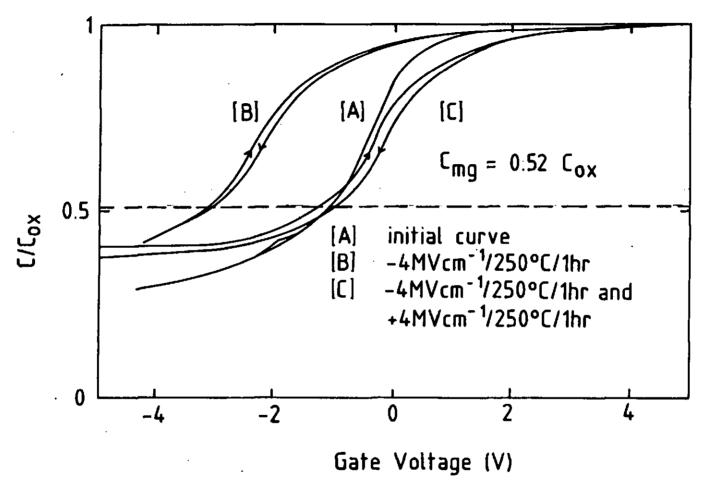

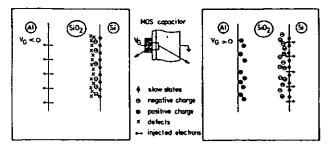

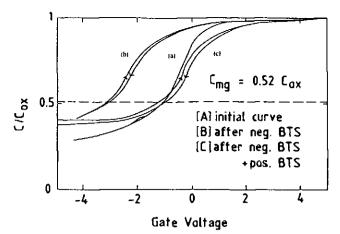

Figure 1.9 shows typical high frequency C-V curves measured following various BTS treatments. After negative BTS (curve (B)) there is a negative shift of the C-V curve due to  $Q_{\rm ot}(+)$  and a distortion relative to the initial curve (curve (A)) due to  $Q_{\rm it}$ . The hysteresis is indicative of some generation of slow-states.  $Q_{\rm ot}(+)$  shows many similarities to  $Q_{\rm f}$  already present in the oxide.

For example, for a given set of BTS conditions the magnitude of  $Q_{\rm ot}(+)$  generated is proportional to  $Q_{\rm f}$  (58). It has been suggested that the two types of charge may be due to the same or similar defects. However, they do show some different behaviour, for example, with respect to low temperature annealing (62). The number of interface states generated during negative BTS appears to be proportional to the initial interface state density,  $D_{\rm it}({\rm init})$  (64). Hence these defects are probably also very similar to each other.

Figure 1.9 Shifts in the high frequency C-V curve after various bias-temperature stresses.

Applying a positive BTS after the negative one (curve (C)) returns the C-V curve to more positive voltages. The distortion of the curve is greater, however, indicating considerable interface degradation. Positive BTS alone results in at most a very small shift to positive voltages (63), indicative of electron trapping. Some interface state generation also occurs.

#### INTRODUCTION

Despite extensive studies of both the kinetics and the processing dependence of the negative bias instability (considered in 4A.1 and 4A.2 respectively), the mechanism of positive charge generation is uncertain. Various models have been proposed, the most important being hole trapping (65) or electron emission from traps in the oxide (66), the breaking of weak bonds associated with the already partially ionised silicon atoms near the interface (58) and the formation and migration of oxygen vacancies (68). These are discussed in more detail in 4A.3. To try to shed more light on these models, the avalanche hole injection technique (outlined in 2.3.3) was used before and after various stresses in an attempt to elucidate any role hole traps might play in positive charge generation during negative BTS.  $Q_{ot}(+)$  was in fact found to be due to filling of intrinsic hole traps i.e traps already present in the oxide before it was subjected to BTS (4B.2). Interface state generation and relationship to hole trapping was also examined (48.3) and a kinetic study of the voltage shift of the C-V curve during BTS was carried out (4B.1).

# CHAPTER TWO: EXPERIMENTAL TECHNIQUES AND ANALYSIS

#### 2.1 Sample Preparation.

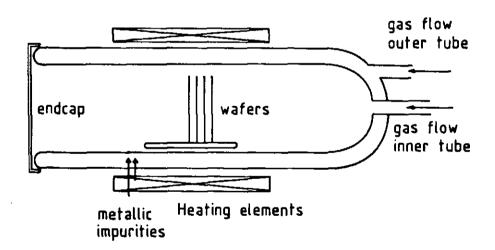

Oxides were grown at 850-1000°C to thicknesses of between 10 and 60 nm on both n- and p- type <100> silicon wafers.  $10^{15}$  or  $10^{17}$  /cm<sup>3</sup> doping was used, the heavily doped material being to ensure laterally homogeneous injection during avalanche injection measurements. Most wafers were processed in a double-walled oxidation tube (Fig.2.1) to reduce the number of medium field breakdowns (21). The oxidation ambient was usually dry oxygen ( $O_2$ ) with  $O_2$  plus <1% trichloroethane (C33) in the outer tube. In most cases, a short POA (about 10 mins.) was carried out in  $N_2$ .

Figure 2.1 Cross section of a double-walled oxidation tube. Metal impurities are removed by the gas flow in the outer tube.

Key processing details for each of the wafers used in this work are shown in Table 2.1 on the following three pages. Aluminium deposition was by d.c. magnetron sputtering or flash evaporation from a tungsten boat. After definition of the electrodes by standard wet lithography, a post-metallisation anneal was carried out in forming gas at 435°C

| WAFER<br>COOE | SUBSTRATE<br>DOP ING | OXIDATION<br>CONDITIONS                                | POA                | ELECTRODE<br>MATERIAL      |

|---------------|----------------------|--------------------------------------------------------|--------------------|----------------------------|

| 232X          | p/1E15               | 52 nm/900°C/2%HCl<br>(GEC)                             | 15" N <sub>2</sub> | 1μ Al/Si<br>mag. sputt.    |

| HI            | n/1E15               | 25 nm/900°C/dry 0 <sub>2</sub>                         | 10" N <sub>2</sub> | 1μ Al<br>mag. sputt.       |

| JN1           | n/1E15               | 31 nm/850°C/dry 0 <sub>2</sub>                         |                    | 1μ Al<br>mag. sputt.       |

| DP2           | p/1E15               | 35 nm/900°C/dry 0 <sub>2</sub>                         | 10" N <sub>2</sub> | 1μ Al<br>mag. sputt.       |

| L9            | n/1E15               | 39 nm/900°C/dry O <sub>2</sub><br>(DWO)                | 10" N <sub>2</sub> | $1\mu$ Almag. sputt.       |

| MN2           | n/1E15               | 39 nm/900°C/dry 0 <sub>2</sub>                         | 10" N <sub>2</sub> | 1μ Al<br>mag. sputt.       |

| MN6           | n/1E17               | 39 nm/900°C/dry 0 <sub>2</sub>                         | 10" N <sub>2</sub> | 1μ Al/Si<br>mag. sputt.    |

| MP2           | p/1E15               | 39 nm/900°C/dry 0 <sub>2</sub>                         | 10" N <sub>2</sub> | 1µ Al/Si<br>mag. sputt.    |

| MP6           | p/1E17               | 39 nm/900°C/dry 0 <sub>2</sub>                         | 10" N <sub>2</sub> | 1μ Al/Si<br>mag. sputt.    |

| P4A3          | n/1E15               | 38 nm/900°C/dry O <sub>2</sub><br>(DWO)                | 10" N <sub>2</sub> | Poly 440 nm<br>I/I P 1E16  |

| P512          | n/1E15               | 29 nm/900°C/dry 0 <sub>2</sub><br>(DWO:0.2% C33 O.T.)  | 10" N <sub>2</sub> | Poly 440 nm<br>P diffusion |

| S02           | n/1E15               | 31 nm/900°C/dry 0 <sub>2</sub> (DWO:0.2% C33 O.T.)     | 10" N <sub>2</sub> | Poly 440 nm<br>I/I P 1E16  |

| U3            | n/1E15               | 59 nm/1000°C/dry 0 <sub>2</sub><br>(DWO:0.2% C33 O.T.) |                    | 1μ Al/Si<br>mag. sputt.    |

| U <b>7</b>    | n/1E15               | 39 nm/900°C/dry 0 <sub>2</sub> (DWO:0.2% C33 O.T.)     |                    | 1μ Al/Si<br>mag. sputt.    |

| 80            | n/1E15               | 39 nm/900°C/dry 0 <sub>2</sub><br>(DWO:0.2% C33 O.T.)  | 10" N <sub>2</sub> | 1µ Al/Si<br>mag. sputt.    |

| U <b>9</b>    | n/1E15               | 27 nm/900°C/dry 0 <sub>2</sub> (DWO:0.2% C33 O.T.)     |                    | 1μ Al/Si<br>mag. sputt.    |

Table 2.2 Summary of wafer processing details (continued overleaf).

## EXPERIMENTAL TECHNIQUES

| U10 | n/1E15 | 28 nm/900°C/dry 0 <sub>2</sub>  | 10" N <sub>2</sub> | 1μ Al/Si    |

|-----|--------|---------------------------------|--------------------|-------------|

|     |        | (DWO:0.2% C33 O.T.)             |                    | mag. sputt. |

| U11 | n/1E15 | 12 nm/900°C/dry 0 <sub>2</sub>  |                    | 1μ Al/Si    |

|     |        | (DWO:0.2% C33 O.T.)             |                    | mag. sputt. |

| U12 | n/1E15 | 12 nm/900°C/dry 0 <sub>2</sub>  | 10" N <sub>2</sub> | lu Al/Si    |

|     |        | (DWO:0.2% C33 O.T.)             |                    | mag. sputt. |

| 13N | n/1E15 | 25 nm/900°C/dry 0 <sub>2</sub>  | 10" N2             | Poly 450 nm |

|     |        | (DWO:0.2% C33 O.T.)             |                    | B diffusion |

| A11 | n/1E15 | 45 nm/900°C/dry 02              | 10" N2             | 15 nm Al    |

|     |        | (DWO:0.2% C33 O.T.)             | _                  | mag. sputt. |

| В6  | n/1E15 | 23 nm/900°C/dry 0 <sub>2</sub>  | 10" N <sub>2</sub> | Poly 450 nm |

|     |        | (DWO:0.2% C33 O.T.)             | _                  | P diffusion |

| CP1 | n/1E15 | 23 nm/900°C/dry 0 <sub>2</sub>  | 10" N <sub>2</sub> | Poly 450 nm |

|     |        | (DWO:0.2% C33 O.T.)             | -                  | P diffusion |

| F6  | n/1E15 | 54 nm/1025°C/dry 0 <sub>2</sub> | 15" N <sub>2</sub> | Poly 450 nm |

|     |        | (DWO:0.2% C33 O.T.)             | -                  | P diffusion |

| ST1 | n/1E15 | 28 nm/900°C/dry 0 <sub>2</sub>  | 10" N <sub>2</sub> | 15 nm Al    |

|     |        | (DWO:0.2% C33 O.T.)             | _                  | mag. sputt. |

| ST2 | n/1E17 | 28 nm/900°C/dry 0 <sub>2</sub>  | 10" N2             | 1μ Al/Si    |

|     |        | (DWO:0.2% C33 O.T.)             | _                  | mag. sputt. |

| S1  | n/1E17 | 51 nm/950°C/dry 02              | 10" N2             | 1µ Al       |

|     |        | (DWO:0.2% C33 O.T.)             | _                  | mag. sputt. |

| S2  | n/1E17 | 51 nm/950°C/dry 0 <sub>2</sub>  | 10" N2             | 500 nm Al   |

|     |        | (DWO:0.2% C33 O.T.)             | _                  | mag. sputt. |

| S3  | n/1E17 | 51 nm/950°C/dry 0 <sub>2</sub>  | 10" N <sub>2</sub> | 250 nm Al   |

|     |        | (DWO:0.2% C33 O.T.)             | . <b>-</b>         | mag. sputt. |

| S4  | n/1E17 | 51 nm/950°C/dry 0 <sub>2</sub>  | 10" N <sub>2</sub> | 125 nm Al   |

|     |        | (DWO:0.2% C33 O.T.)             | _                  | mag. sputt. |

| S5  | n/1E17 | 51 nm/950°C/dry 0 <sub>2</sub>  | 10" N <sub>2</sub> | 50 nm Al    |

|     |        | (DWO:0.2% C33 O.T.)             | _                  | mag. sputt. |

| s6  | n/1E17 | 51 nm/950°C/dry 02              | 10" N <sub>2</sub> | 15 nm Al    |

|     |        | (DWO:0.2% C33 O.T.)             | _                  | mag. sputt. |

|     |        | •                               |                    | _           |

Table 2.2 (cont'd) Summary of wafer processing details.

| T1          | n/1E15 | 80 nm/950°C/dry 0 <sub>2</sub>                        | 10" N <sub>2</sub> | 15 nm Al<br>mag. sputt. |

|-------------|--------|-------------------------------------------------------|--------------------|-------------------------|

| T2          | n/1E15 | (DWO:0.2% C33 O.T.)<br>80 nm/950°C/dry O <sub>2</sub> | 10" N <sub>2</sub> | 60 nm Al                |

|             |        | (DWO:0.2% C33 O.T.)                                   | 10 112             | mag. sputt.             |

| Т3          | n/1E15 | 80 nm/950°C/dry 0 <sub>2</sub>                        | 10" N2             | 1μ Al                   |

|             |        | (DWO:0.2% C33 O.T.)                                   | _                  | mag. sputt.             |

| т6          | n/1E15 | 12 nm/950°C/dry 0 <sub>2</sub>                        | 10" N2             | Tμ Al/Si                |

|             |        | (DWO:0.2% C33 O.T.)                                   |                    | mag. sputt.             |

| Т9          | n/1E15 | 21 nm/950°C/dry 0 <sub>2</sub>                        | 10" N <sub>2</sub> | 1μ Al/Si                |

|             |        | (DWO:0.2% C33 O.T.)                                   |                    | mag. sputt.             |

| T12         | n/1E15 | 49 nm/950°C/dry 0 <sub>2</sub>                        | 10" N2             | 1μ Al/Si                |

|             |        | (DWO:0.2% C33 O.T.)                                   |                    | mag. sputt.             |

| R1          | n/1E17 | 58 nm/950°C/dry O <sub>2</sub>                        | 10" N2             | Poly 450 nm +           |

|             | •      | (DWO:0.2% C33 O.T.)                                   |                    | 1μ sputt.               |

| R2          | n/1E17 | 58 nm/950°C/dry O <sub>2</sub>                        | 10" N <sub>2</sub> | Poly 450 nm +           |

|             |        | (DWO:0.2% C33 O.T.)                                   |                    | 425 nm sputt.           |

| R3          | n/1E17 | 58 nm/950°C/dry 0 <sub>2</sub>                        | 10" N <sub>2</sub> | Poly 450 nm +           |

|             |        | (DWO:0.2% C33 O.T.)                                   |                    | 100 nm sputt.           |

| R4          | n/1E17 | 58 nm/950°C/dry O <sub>2</sub>                        | 10" N <sub>2</sub> | Poly 450 nm +           |

|             |        | (DWO:0.2% C33 O.T.)                                   |                    | 850 nm flash            |

| R5          | n/1E17 | 58 nm/950°C/dry 0 <sub>2</sub>                        | 10" N <sub>2</sub> | Poly 450 nm +           |

|             |        | (OWO:0.2% C33 O.T.)                                   |                    | 425 nm flash            |

| R6          | n/1E17 | 58 nm/950°C/dry 0 <sub>2</sub>                        | 10" N <sub>2</sub> | Poly 450 nm +           |

|             |        | (OWO:0.2% C33 O.T.)                                   |                    | 100 nm flash            |

| R7          | n/1E17 | 58 nm/950°C/dry 0 <sub>2</sub>                        | 10" N <sub>2</sub> | Poly 450 nm +           |

| _           |        | (DWO:0.2% C33 O.T.)                                   |                    | no metal                |

| R8          | n/1E17 | 58 nm/950°C/dry 0 <sub>2</sub>                        | 10" N <sub>2</sub> | 850 nm Al               |

|             |        | (OWO:0.2% C33 O.T.)                                   |                    | mag. sputt.             |

| R10         | n/1E17 | 58 nm/950°C/dry 0 <sub>2</sub>                        | 10" N <sub>2</sub> | 850 nm Al               |

| <b>D.</b> - |        | (OWO:0.2% C33 O.T.)                                   |                    | flash evap.             |

| R12         | n/1E17 | 58 nm/950°C/dry 0 <sub>2</sub>                        | 10" N <sub>2</sub> | 425 nm Al               |

| 2.0         | 14.994 | (DWO:0.2% C33 O.T.)                                   |                    | flash evap.             |

| R13         | n/1E17 | 58 nm/950°C/dry 0 <sub>2</sub>                        | 10" N <sub>2</sub> | 100 nm Al               |

|             |        | (DWO:0.2% C33 O.T.)                                   |                    | flash evap.             |

Table 2.2 (cont'd) Summary of wafer processing details.

#### EXPERIMENTAL TECHNIQUES

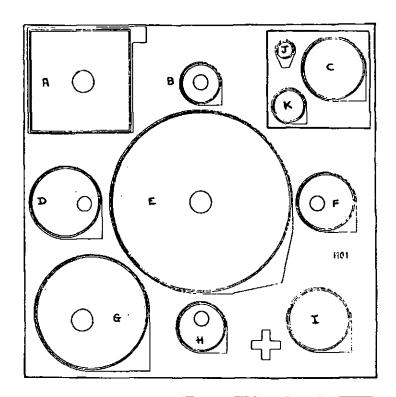

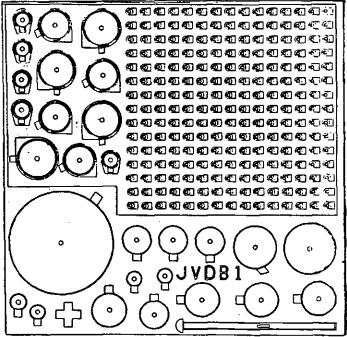

for 20 mins. Polysilicon gates were formed by LPCVD of polysilicon (450 nm) which was then thermally doped with POCl<sub>3</sub> or ion-implanted with boron or phosphorus. Aluminium was then deposited on top of the polysilicon to ensure good contact. Capacitors of various sizes were defined using one of the two sets of masks illustrated in Fig.2.2. The capacitor dimensions are shown in Table 2.2 for the case of thin oxide only and when using a thick field oxide. The capacitor area is reduced slightly in the latter case by the area of the central contact pad which covers thick oxide rather than thin oxide. Most of the devices measured were processed at ESAT, K.U.Leuven. However, wafer 232X in Table 2.1 was part of a batch made at GEC Hirst Research Centre, Wembley.

|   | Capacitor      | Thin Oxide Only         | Thin Oxide + Field Oxide |

|---|----------------|-------------------------|--------------------------|

|   | Code           | Area (cm²)              | Area (cm <sup>2</sup> )  |

| - | ~~~ <b>~~~</b> |                         |                          |

|   | Α              | $4.42 \times 10^{-3}$   | $4.11 \times 10^{-2}$    |

|   | В              | $4.91 \times 10^{-4}$   | $3.74 \times 10^{-4}$    |

|   | С              | $1.26 \times 10^{-3}$   | 1.26 x 10 <sup>-3</sup>  |

|   | 0              | $1.66 \times 10^{-3}$   | 1.51 x 10 <sup>-3</sup>  |

|   | E              | 1.15 x 10 <sup>-2</sup> | 1.11 x 10 <sup>-2</sup>  |

|   | F              | $1.08 \times 10^{-3}$   | $9.39 \times 10^{-4}$    |

|   | G              | $4.41 \times 10^{-3}$   | $4.12 \times 10^{-3}$    |

|   | Н              | $7.54 \times 10^{-4}$   | $6.28 \times 10^{-4}$    |

|   | I              | $1.26 \times 10^{-3}$   | (Field oxide only)       |

|   | J              | 7.85 x 10 <sup>-5</sup> | 7.85 x 10 <sup>-5</sup>  |

|   | K              | $3.14 \times 10^{-4}$   | $3.14 \times 10^{-4}$    |

|   | L              | $4.82 \times 10^{-4}$   | 4.82 x 10 <sup>-4</sup>  |

|   | M              | 1.96 X 10 <sup>-5</sup> | 1.96 x 10 <sup>-5</sup>  |

|   |                |                         |                          |

Table 2.2 Dimensions of capacitors on masks 1 and 2 in Figure 2.2.

Figure 2.2 Photolithography masks used to define caps. of various areas, with and without a field oxide. Mask 2 has caps. B,F,G,H,J and K of mask 1 plus the rectangular cap., L and an array of small caps., M.

#### 2.2 Breakdown measurements.

Constant voltage wearout and fast voltage ramp (dielectric strength) breakdown measurements were both carried out on an automatic measurement system. This is controlled by an HP 9835 desk top computer via an IEEE bus and includes a Karl Suss wafer probe station and a multi-probe breakdown detection system built at ESAT. Before describing this system in more detail some of the problems associated with breakdown measurements will be considered.

# 2.2.1 Dielectric strength.

A fast voltage ramp is generally applied to a capacitor in order to measure the dielectric strength of the insulator i.e. the field at which it would break down on instantaneous application of the voltage. Ideally an infinitely fast ramp would be used so that no wearout could occur during the measurement and the true time-zero breakdown would be measured. In practice, however, the need for a reliable means of breakdown detection limits the ramp rate which can be used. Usually, breakdown is defined experimentally as the exceeding of a preset current. The voltage ramp must therefore cause only a small displacement current relative to this set current. The response time of the measuring circuit and the accuracy required in measurement of the breakdown voltage must also be considered.

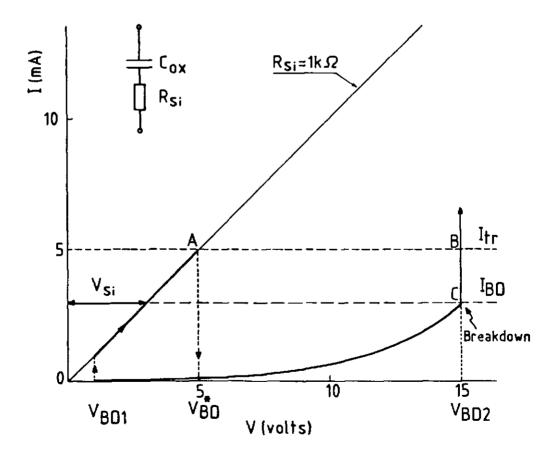

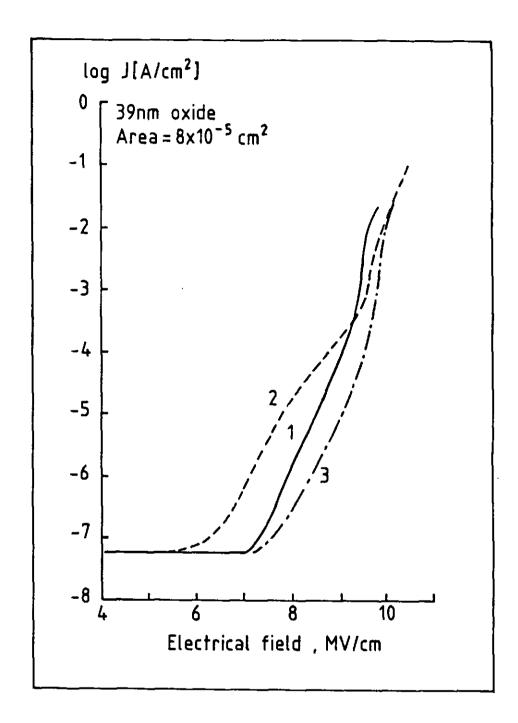

The current chosen to define breakdown,  $I_{\rm tr}$ , is an extremely important parameter (69). In the high field part of the breakdown distribution very large currents may flow prior to catastrophic failure (up to ~60 A/cm² was measured on 8 x  $10^{-5}$  cm² samples). If the current at breakdown,  $I_{\rm BO}$ , is high a large trigger current must be chosen to ensure the capacitor is actually broken down. Under these conditions a relatively large voltage drop across the substrate (and any resistance in the measurement circuit) has to be taken into account. This is  $V_{\rm Si}$  in Fig.2.3.  $V_{\rm Si}$  will be especially

significant for thin oxides and low substrate dopings. For high field breakdowns it is simply a matter of subtracting  $V_{Si}$  from the measured breakdown voltage. All low field breakdowns occurring below  $I_{tr}.R_{Si}$  (=  $V_{BD}^*$ ) will be measured as  $V_{BD}^*$ , however (see Fig.2.3). Hence it is not always possible to observe high and low field breakdowns simultaneously. The recently proposed technique (7D) in which a high voltage pulse is followed by a lower voltage leakage test avoids the problem of choosing an appropriate set current but the parasitic voltage drop must still be taken into account. Harari (8) applied a high constant current stress to his samples and measured the time-to-breakdown,  $t_{bd}$  and also the applied voltage. Extrapolation of a plot of  $t_{bd}$  versus I to zero time gave  $I_{BD}$ .  $V_{BD}$  could be calculated from this technique via the equation for F-N tunneling.

Figure 2.3 Effect of series resistance and trigger current on the breakdown voltage in a dielectric strength measurement.

## 2.2.2 Time dependent dielectric breakdown.

Time dependent dielectric breakdown (TDDB) orwearout measurements may be conducted by applying either a constant current or constant voltage stress to the sample and monitoring the time at which sample breaks down. These measurements are by their nature time consuming and it is advantageous to be able to examine several devices simultaneously. The multi-probe system described below allows 36 capacitors to be stressed at the same time under constant voltage Constant current measurements were only conducted on individual devices. This could be done in either of two ways. avalanche injection system (described in section 2,3.5) a variable d.c. voltage could be used in place of the sawtooth waveform. Alternatively, a Keithley 220 programmable constant current source was available for use in conjunction with an HP 3456A digital voltmeter. These devices were also controlled by the HP 9835A computer and this system allowed times-to-breakdown as low as 3 ms to be measured and hence high current stresses to be applied. I-V curves could also be measured using this configuration.

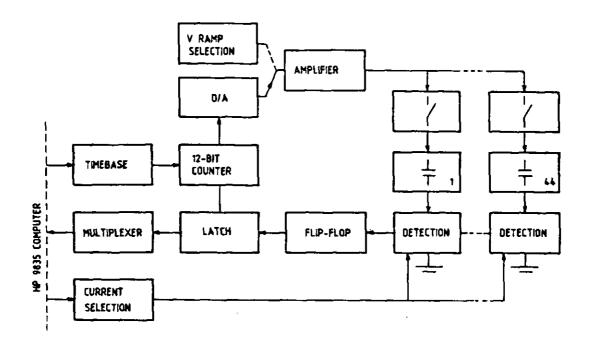

## 2.2.3 Multi-probe breakdown detection system.

A block diagram of this system is shown in Fig.2.4. The voltage source (-100V to +100V) has a measurement accuracy of 25 mV and five possible sweep rates: 2.5, 5, 10, 25, 50 and 100 V/s. The reference current can be chosen over the range from 0.08 to 5 mA. Time can be measured up to 174 min with an accuracy of 0.01 seconds. Therefore, both wearout and fast voltage ramp measurements may be performed on this system.

Each measurement consists of several cycles during which all 36 capacitors are tested. For dielectric strength measurements the value of the applied voltage is determined by a time base, a 12-bit counter and a D/A converter. The voltage is incremented by 25 mV at each clock pulse. The length of this pulse is variable from 250 to 10  $\mu$ s.

Figure 2.4 Block diagram of the multi-probe breakdown detection system.

Thus, sweep rates from 2.5 V/s to 100 V/s can be obtained. When one or more capacitors exceed the reference current during a voltage step a flip-flop corresponding to that capacitor is set and an interrupt is sent to the microprocessor. At the end of each voltage step the applied voltage and the state of all the flip-flops are read into the microprocessor. Broken-down oxides are immediately disconnected from the voltage source. Before the voltage is incremented again all the flip-flops are reset, the data is processed by the microprocessor and the next measurement cycle begins.

For wearout measurements a constant voltage is applied to the capacitors and on breakdown the time instead of the voltage is read in. The 12-bit counter is extended to a 20-bit counter for these measurements to increase the maximum time which can be registered to 174 minutes.

#### 2.3 Charge injection and sensing techniques.

Three techniques were available to inject charge into MOS capacitors. The first of these was simply the application of a high field to the oxide which results in current flow by F-N tunneling. Tunneling injection has been used for charge trapping studies (71,72,73) but the requirement for high fields to inject relatively low current densities is a disadvantage for this purpose. Field ionisation of trapped charge and breakdown of the SiO<sub>2</sub> are favoured under these conditions. In this work high field stressing was used primarily to simulate the conditions existing immediately prior to breakdown of the insulator. Charge was injected under constant current conditions, the voltage being adjusted to compensate for carrier trapping in the oxide. The charge which could be passed prior to breakdown, Q<sub>bd</sub>, was also measured in this way.

Avalanche injection of both electrons (34,74) and holes (75) was used to charge traps in the oxide. Relatively large current densities can be injected into the  $SiO_2$  by this method at moderate oxide fields ( $\leq$ 4 MV/cm) enabling the detection of traps with small capture probabilities. The low fields used also limit further damage to the oxide and make detrapping of charge less likely.

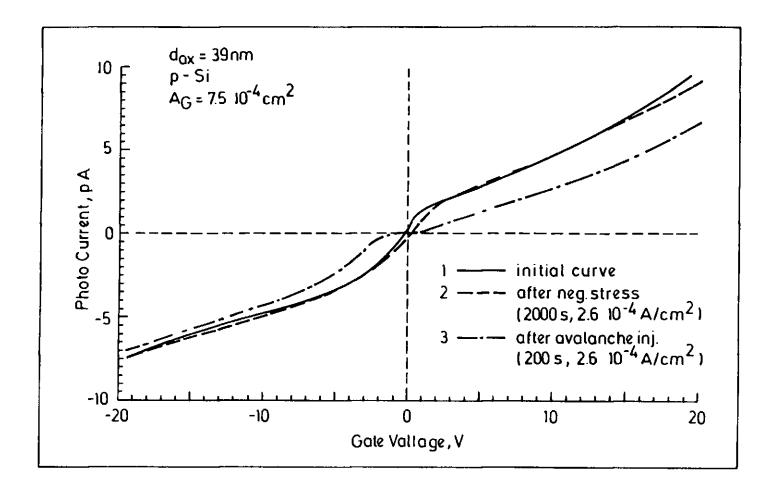

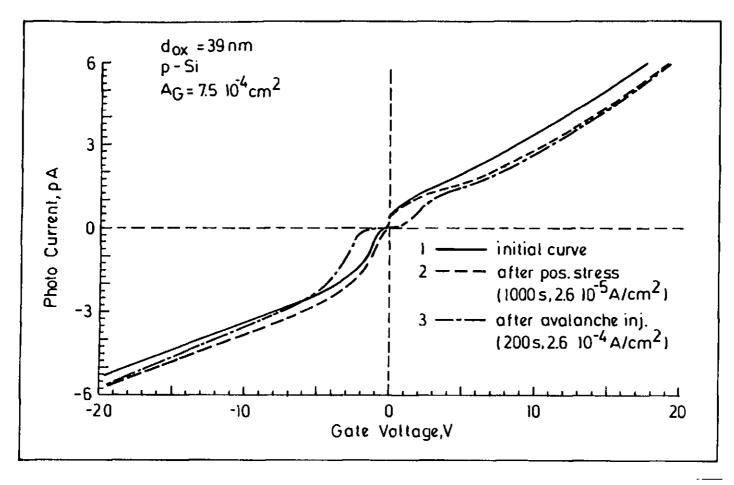

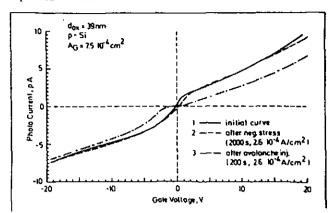

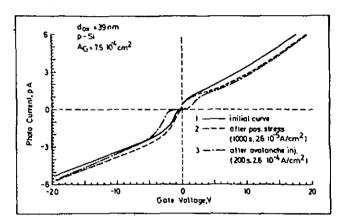

The third charge injection technique used was internal photoemission or photo I-V (76,77). This allows the injection of low current densities at low to moderate fields and the I-V curve obtained is very sensitive to the charge distribution in the oxide. It was used to determine the centroid and density of trapped oxide charge (35).

These three techniques and the experimental set-up used to conduct the measurements are described in greater detail in the following sections.

# 2.3.1 Fowler-Nordhelm tunneling.

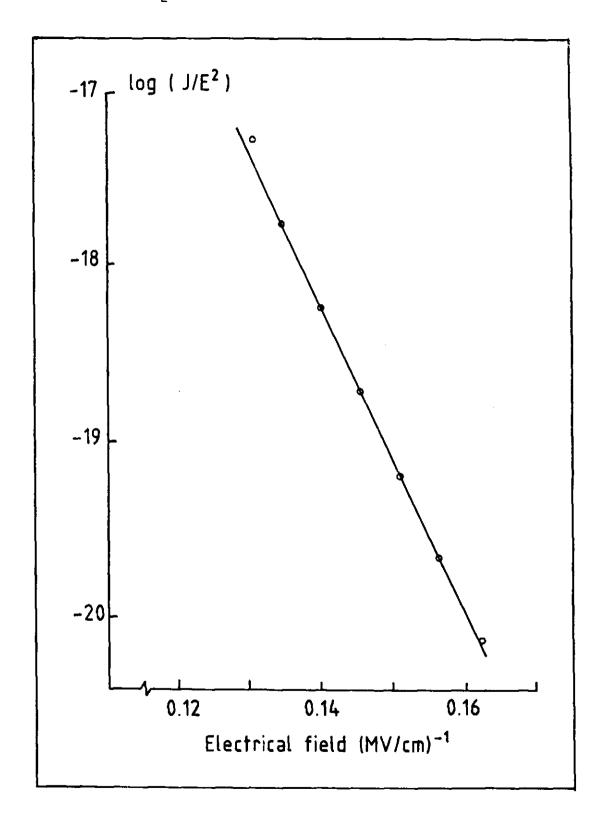

On application of fields above ~6MV/cm substantial current begins to flow through an MOS capacitor. From the dependence of the current density on the applied field (log  $(J/E^2) \propto 1/E$ ) conduction would seem to be due to F-N tunneling of electrons through the triangular barrier at the interface into the oxide conduction band (12). The complete expression for the tunneling current is:

$$J = (q^2 E^2 / 8\pi h \Phi) \exp[-4(2m^*)^{0.5} \Phi^{1.5} / 3q h E]$$

(2.1)

where h is Planck's constant,  $\bar{h}$  is  $h/2\pi$ , q the charge on the electron, E the electric field,  $\Phi$  the barrier height and  $m^*$  the effective mass of the electron (usually taken as 0.5 m, where m is the free electron mass).

If the effect of the image force on the barrier is taken into account, two correction factors t(y) and v(y) are introduced into the Fowler-Nordheim equation. These are tabulated integrals (78) dependent on the normalised image-force barrier lowering, y, where:

$$y = (1/\Phi)(q^3E/4\pi\epsilon_{ox})^{0.5}$$

(2.2)

This correction causes an essentially parallel shift of the theoretical F-N plot to higher values of  $J/E^2$ .

Although tunneling is itself temperature independent the number of electrons incident on the barrier depends on the temperature. This introduces a term  $\pi ckT/\sin(\pi ckT)$  where  $c=2(2m^*\phi)^{0.5}t(y)/q\hbar E$  into the Fowler-Nordheim equation. The F-N plot is still close to a straight line but with a slightly smaller slope. The tunneling equation including correction factors then becomes:

$$J = (q^{3}E^{2}/8\pi h\Phi)[1/t^{2}(y)][\pi ckT/\sin(\pi ckT)]$$

$$\times \exp\{-[4(2m^{*})^{0.5}\Phi^{1.5}/3q\hbar E].v(y)\}$$

(2.3)

#### EXPERIMENTAL TECHNIQUES

As well as using the F-N tunneling phenomenon for constant current high field stress measurements, ramp I-V curves were also measured. This could be done either by using a ramp voltage source (Sweepy 1, built at ESAT) and logarithmic picoammeter (Keithley 26000) with a Houston 2000 chart recorder or by means of the Keithley 220 programmable current source and HP 3456A digital voltmeter previously described.

## 2.3.2 Avalanche electron injection.

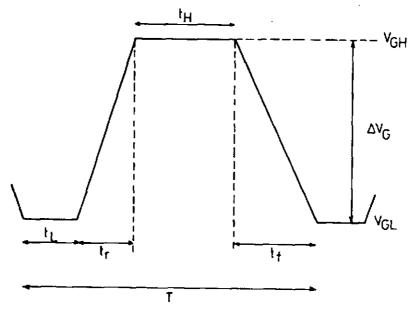

To cause avalanche injection of minority carriers, a periodic waveform is used (sinusoidal, square or sawtooth) to pulse the substrate into deep depletion (34,74). Carriers generated in the depletion layer reach sufficient energies for impact ionisation to occur. Some of the hot carriers thus generated have enough energy to surmount the interfacial barrier and enter the  $\mathrm{SiO}_2$ . Electrons are injected when the substrate is p-type and holes when it is n-type. In this manner charge is injected over part of each pulse cycle. Charge trapping during injection means that to maintain a constant current a feedback circuit must be used to regulate the amplitude of the avalanching pulses. Avalanche injection can be performed only over a limited doping range. Above  $10^{18}$  /cm³ dopant atoms interband tunneling rather than avalanche breakdown occurs. Below -5 x  $10^{16}$  /cm³, depending on the oxide thickness, edge breakdown occurs so that injection is no longer homogeneous (79).

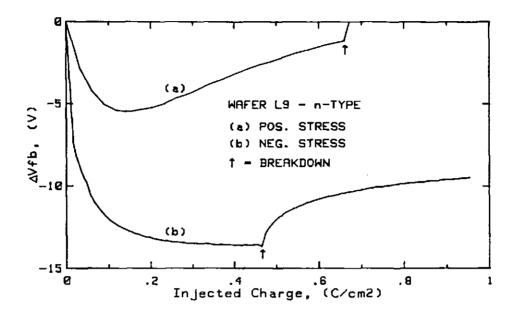

During avalanche injection the flatband voltage shift ( $\Delta V_{fb}$ ) or the midgap voltage shift ( $\Delta V_{mg}$ ) is usually measured as a function of time (and hence of injected charge). Assuming first order trapping kinetics as proposed by Ning and Yu (80), these data can be converted to a set of discrete traps with capture cross sections  $\sigma_i$  and effective trap densities,  $N_i$  according to the following equation:

$$\Delta V_{fb} = \sum_{q} q_{id_{OX}} / \epsilon_{OX} [1 - \exp(-\sigma_{i}jt/q)]$$

$$i=1$$

(2.4)

where  $d_{OX}$  is the oxide thickness, t the injection time and j the current density. The various capture cross sections can be determined from the slope of the linear portions of the  $\ln(d\Delta V_{fb}/dt)$  versus time curve. An alternative more accurate procedure, however, uses the Gauss-Newton method based on Jacobian matrices (81). This is much less sensitive to noise, finds always a least squares fit and is not limited with respect to the number of traps it can fit in one calculation. This method has been implemented in a fitting program written at ESAT<sup>++</sup>.

## 2.3.3 Avalanche hole injection

With an n-type substrate avalanche breakdown results in injection of holes into the SiO<sub>2</sub>. The mechanism is the same as that described for electrons in the previous section. One major problem exists with hole injection, however. This is the possibility of simultaneous injection of electrons from the gate so that the total current is due to both holes and electrons flowing through the sample. It has been shown by Aitken and Young (75) that the use of a sawtooth waveform is necessary to prevent electron injection. This ensures that whenever there is a high oxide field present there is also a displacement current in the silicon. Hence electrons need not be injected from the gate to satisfy current continuity requirements. Recent work has also shown that provided that the change in applied voltage needed to maintain a constant set current tracks the change in the flatband voltage, i.e. that no 'turnaround' effect is observed in the applied voltage, then negligible electron injection is occuring (82).

<sup>\*\*</sup>Program written by M.Heyns.

## 2.3.4 Internal photoemission.

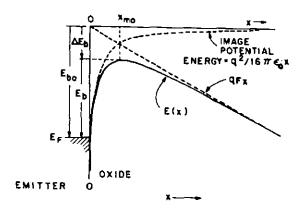

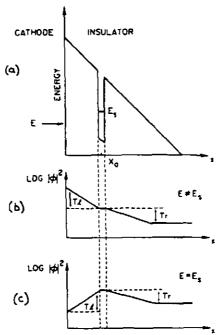

Using a transparent gate electrode, electrons excited by the absorption of u.v. light can be injected into the SiO2 from either the gate or the substrate depending on the polarity of the applied bias (76,77). For an electron to be injected, it must first reach and then surmount the interfacial barrier. The probability of reaching the barrier depends on the likelihood of scattering, which in turn depends on the distance of the potential energy barrier maximum,  $x_{mo}$ , from the injecting interface (Fig.2.5). The probability of electrons surmounting the barrier depends both on the barrier height and on the energy with which they arrive at the barrier. Both the barrier height and position are affected by oxide charge and by the Either the barrier height or its position can be made to dominate by using photon energies close to or considerably greater than the energy barrier, respectively. Oxide charge affects the barrier position much less than its height. However in the barrier height mode photocurrents are low and difficult to detect. The barrier position mode is therefore easier to use in practice.

Figure 2.5 Effect of the image force potential on the potential energy barrier at the injecting interface (after 83).

Difficulties also arise in the analysis of the current characteristics in the barrier height mode since it is not certain whether tunneling through the top of the barrier should be taken into account (84).

Figure 2.5 shows an energy distance diagram of the  $Si-SiO_2$  interface and the effect of the image force potential on the barrier. It can be shown that the position of the barrier maximum,  $x_{mo}$ , in the case of no oxide charge is given by:

$$x_{mo} = (qx_{mo}/16\pi\epsilon_{ox}(V_g - \psi_{ms}))^{0.5}$$

(2.5)

where  $\psi_{\text{mS}}$  is the metal-silicon work function difference (77). Thus, the barrier moves closer to the interface as  $V_{\mathbf{g}}$  is increased.

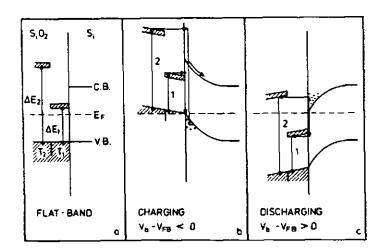

Three cases are distinguishable when oxide charge is present. First if the charge is very close to the interface i.e. before the barrier maximum, the experimental photo I-V curve cannot distinguished from that with no oxide charge present (Fig.2.6a). If the barrier maximum is within the charge distribution, this can be profiled. By varying the gate bias, the barrier maximum is swept through the oxide charge distribution and the resulting photo I-V curve is distorted compared with the case of no oxide charge (Fig. 2.6b). Finally, if there is oxide charge only beyond the barrier maximum then the photo I-V curve is translated along the voltage axis remaining parallel to the curve in the case of no oxide charge (Fig.2.6c). The charge density,  $Q_0$  and the centroid,  $x_0$  can be extracted from the voltage shift measured first with the metal  $(\Delta V_{gm})$  and then with the silicon  $(\Delta V_{gs})$  as the injecting electrode (35), using the following equations:

$$\Delta V_{gs} = Q_o x_o / \epsilon_{ox}$$

(2.5)

$$\Delta V_{gm} = Q_o[(d_{ox} - x_o)/\epsilon_{ox}]$$

(2.6)

where  $\textbf{d}_{\text{O}\,\textbf{X}}$  is the oxide thickness and  $\boldsymbol{\epsilon}_{\text{O}\,\textbf{X}}$  the dielectric constant.

Figure 2.6 Shifts in the photo I-V curves for the case of (a) only interface charge, (b) charge at  $x_{mo}$ , (c) bulk charge. (After (85)).

The photo I-V technique is therefore a valuable means of examining charge distributions in the oxide. Currents may be kept low to avoid further charge trapping and at relatively low light intensities photodepopulation is also avoided.

# 2.3.5 Measurement systems.

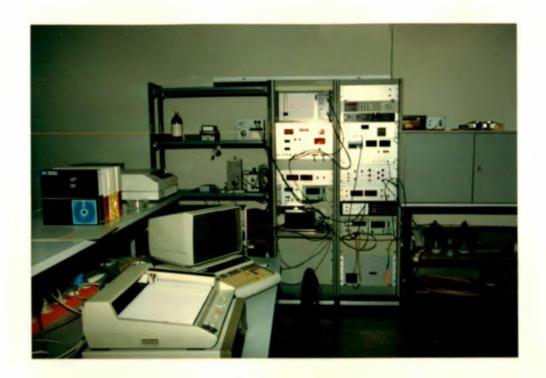

Two automated systems have been developed in ESAT to study charge trapping effects in insulators. These are the avalanche injection and photo I-V systems. Both are connected to the same data acquisition system and HP 9835 controller. A switch allows the sample probe station to be easily connected to either system. A photograph of the measurement equipment is shown in Fig. 2.7.

Figure 2.7 The avalanche and photo I-V measurement systems.

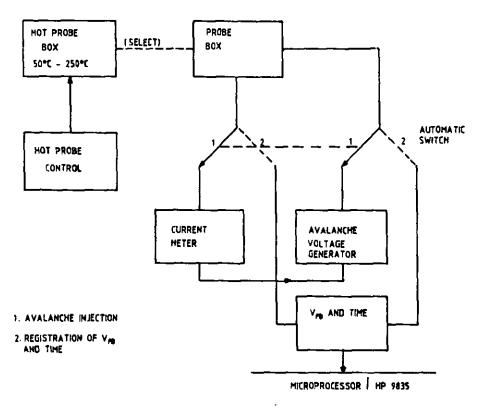

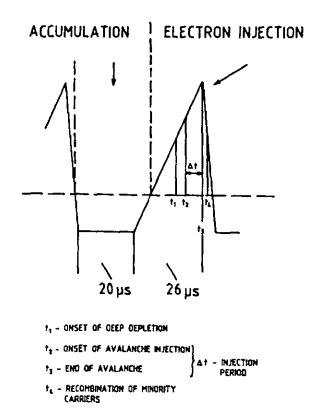

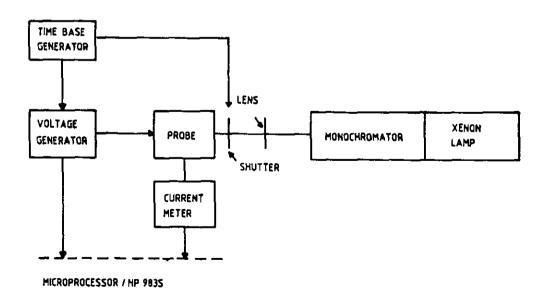

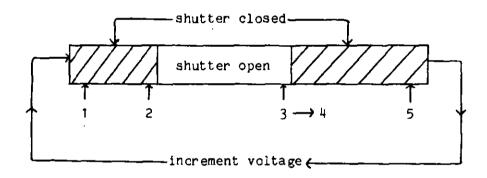

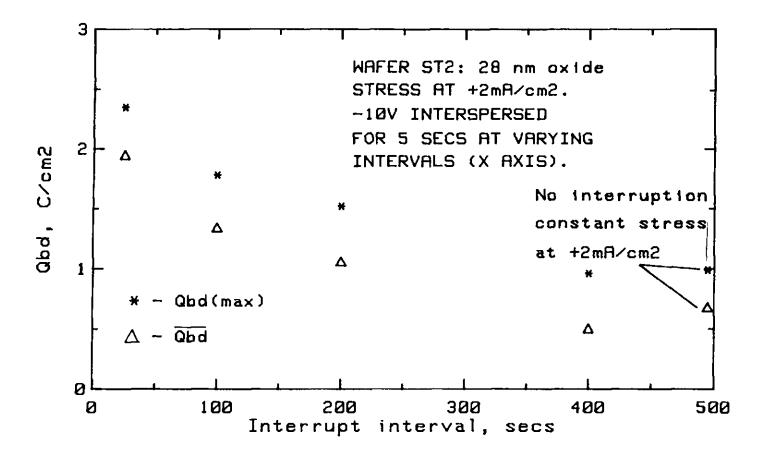

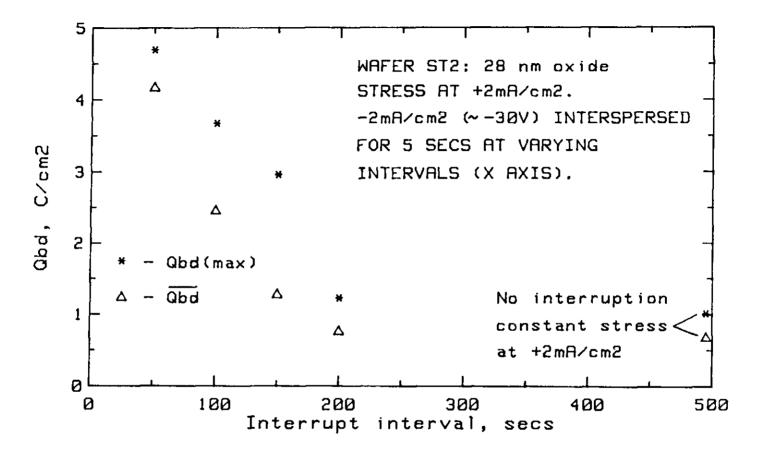

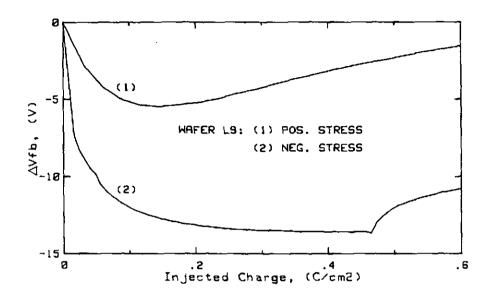

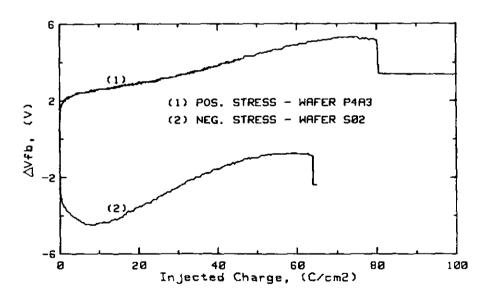

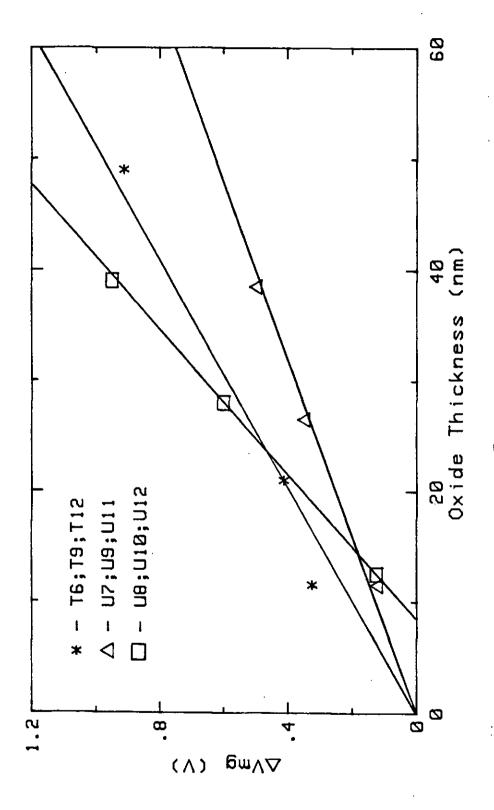

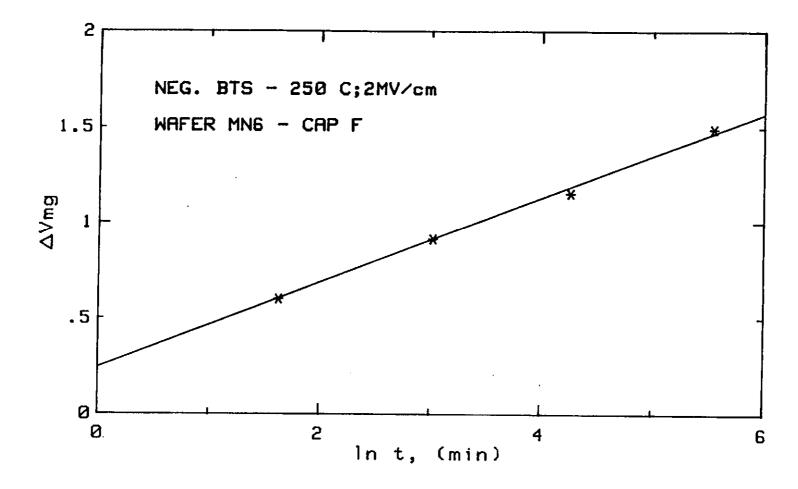

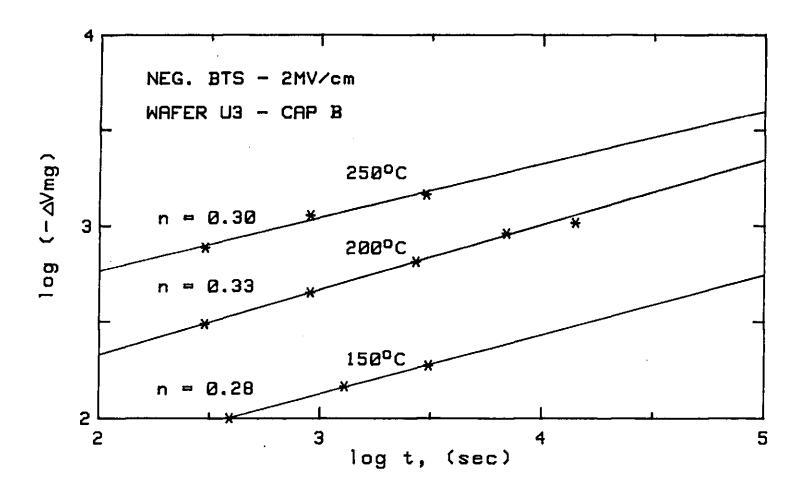

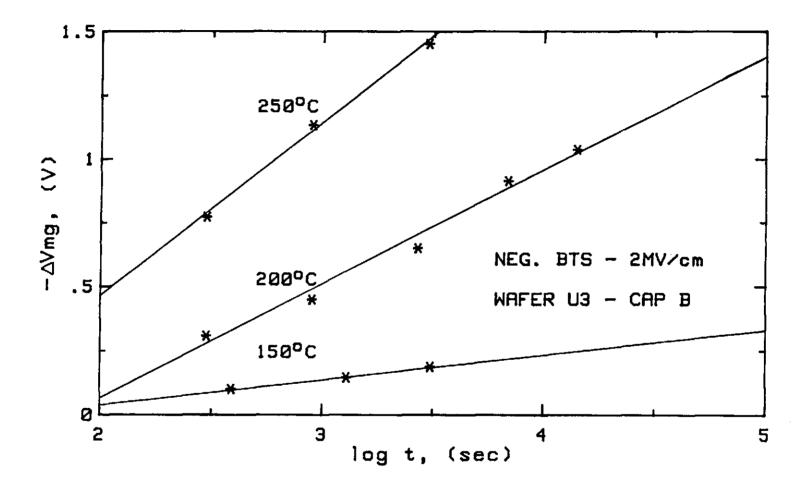

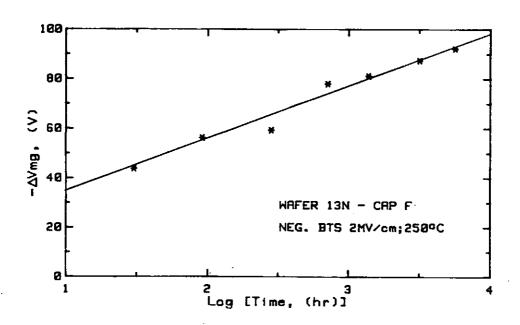

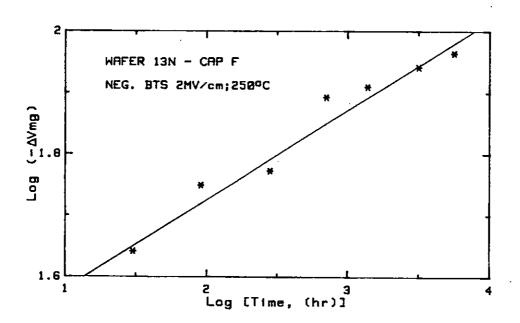

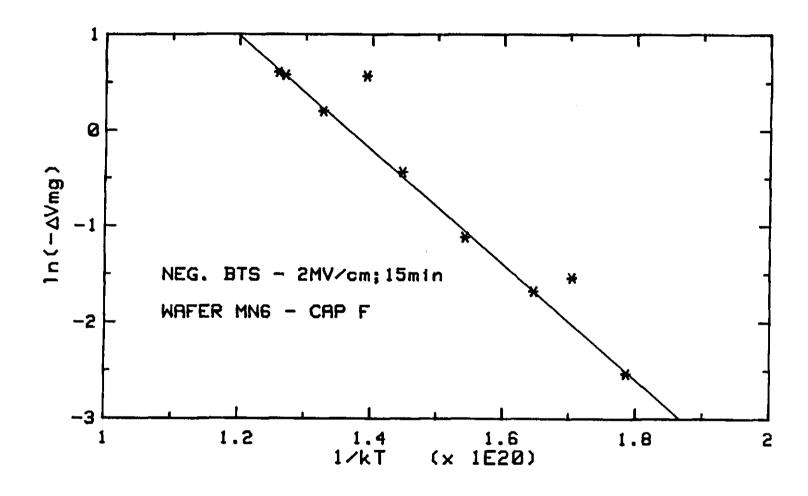

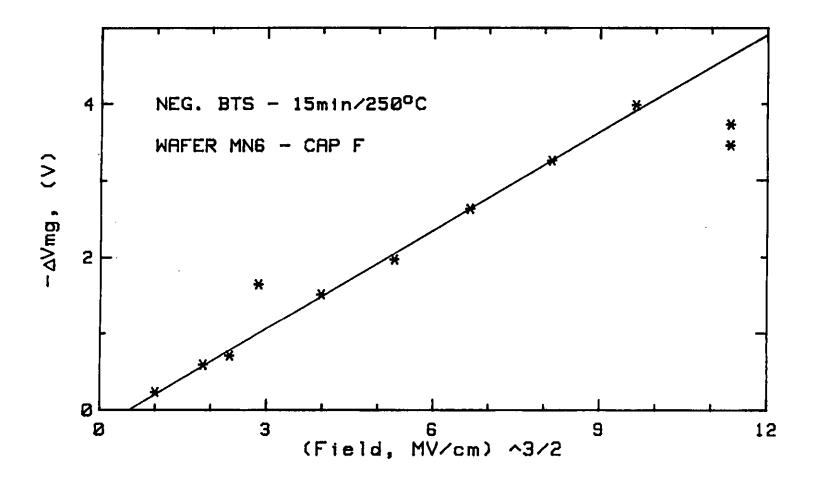

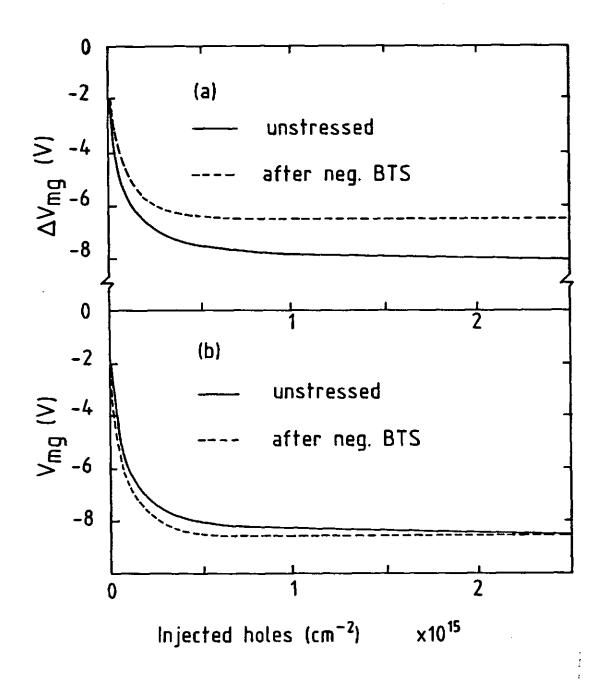

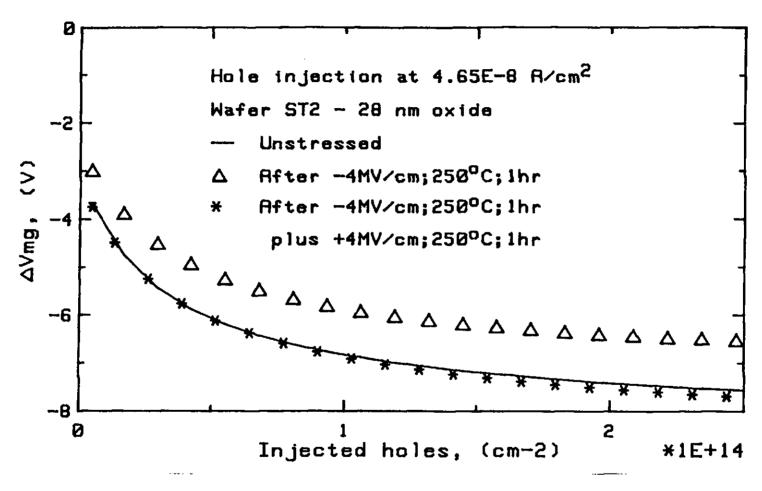

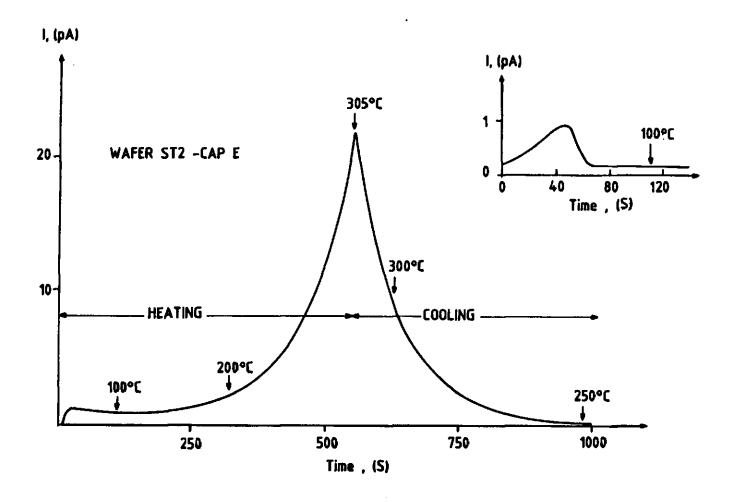

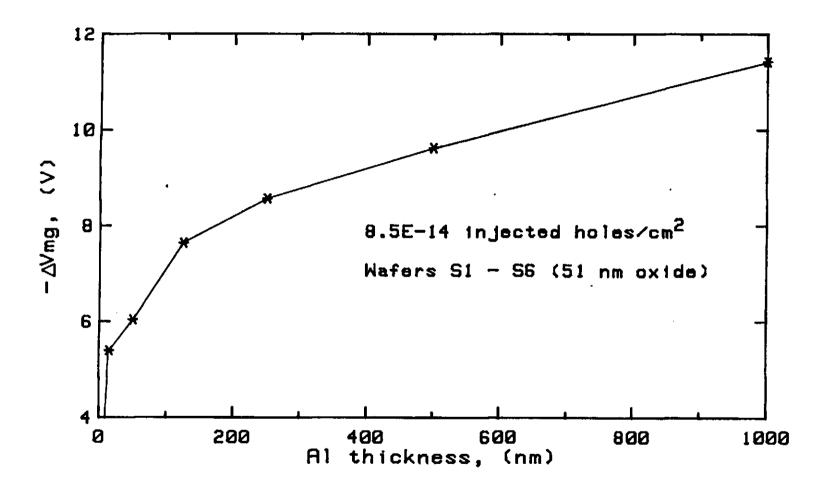

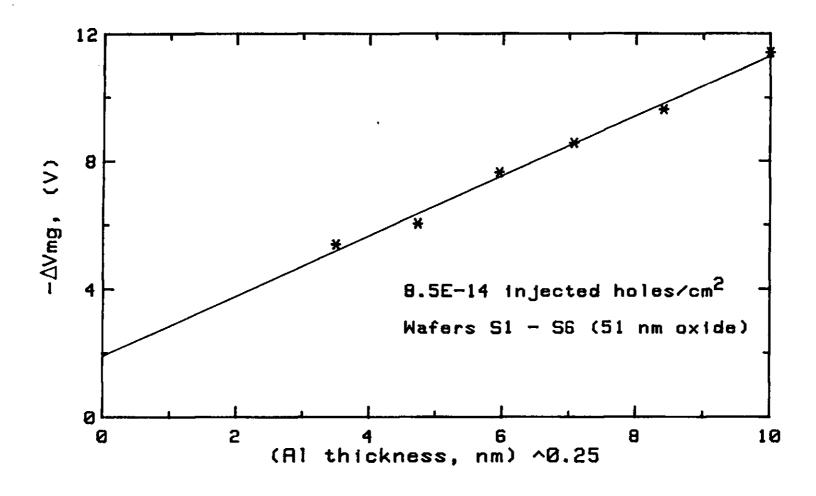

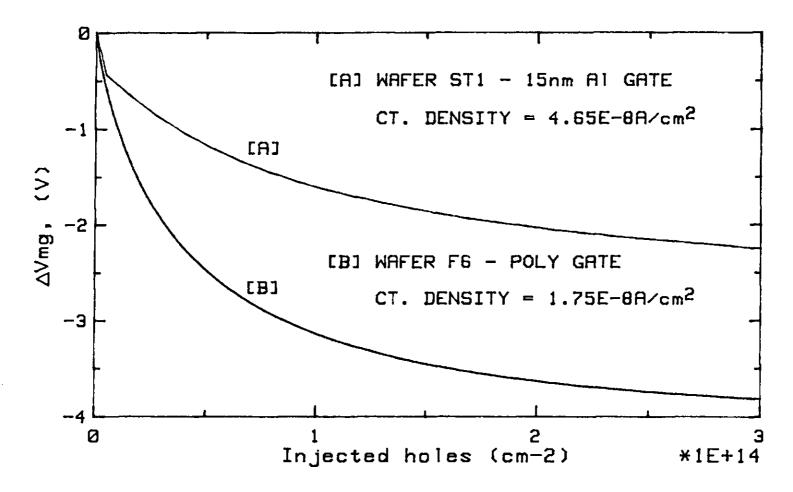

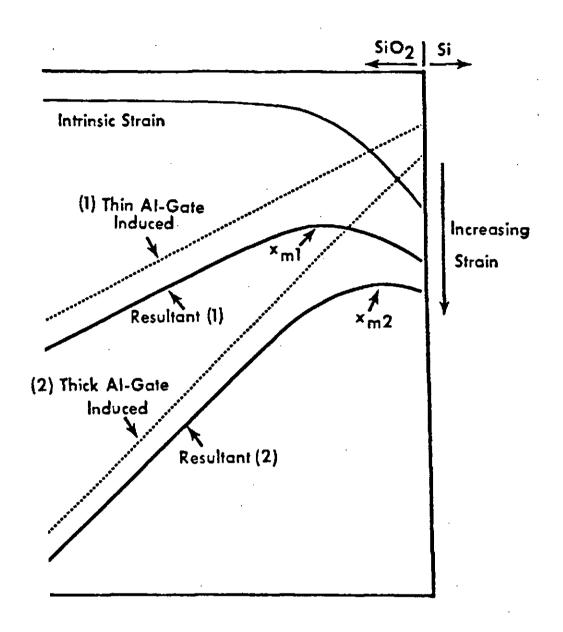

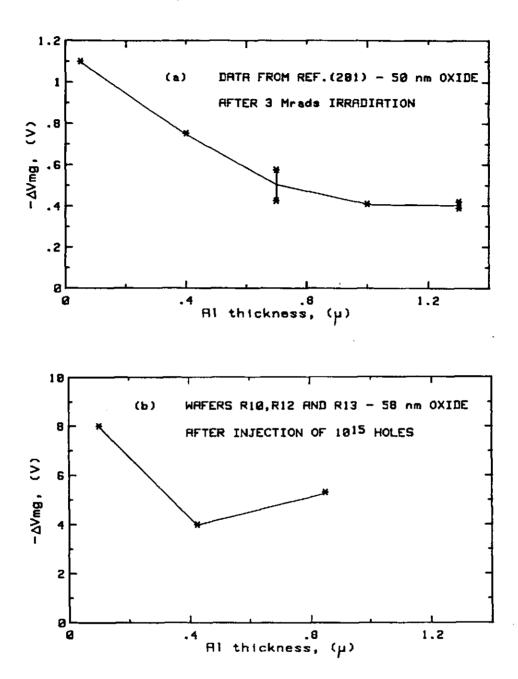

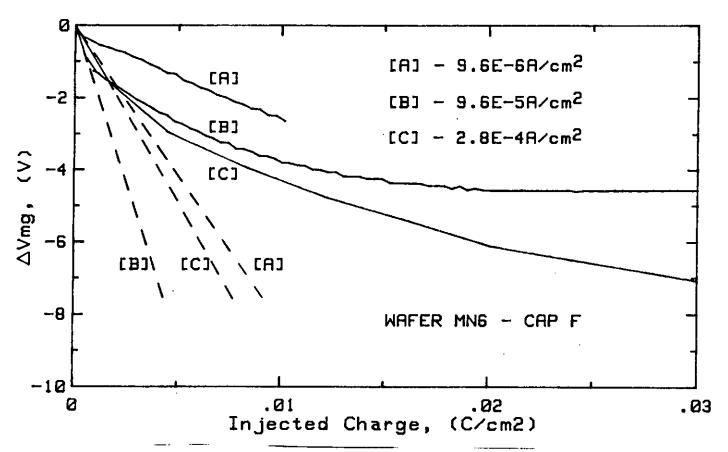

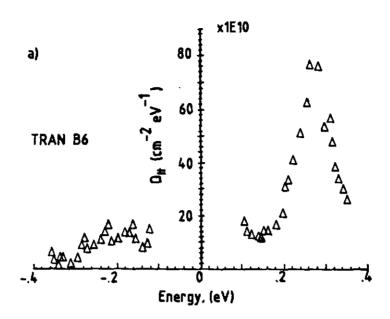

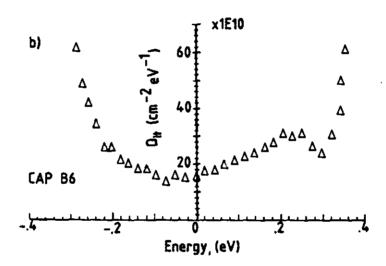

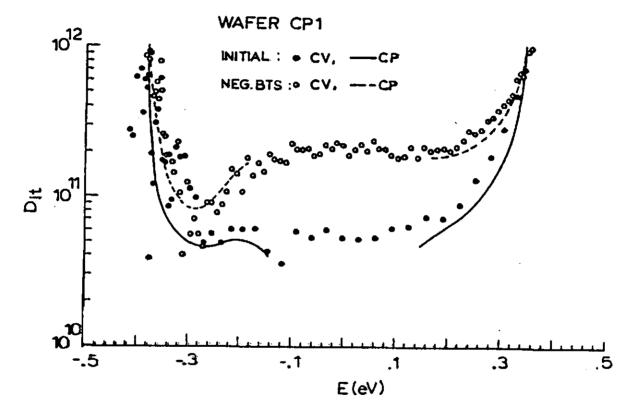

## 2.3.5.1 Avalanche injection system.